By Adam Taylor

目前我们已经开启Zynq开发发现之旅有一段时间了,接下来我们还要去研究Zynq SoC上千兆以太网的性能,这将使你的应用具备网络互连功能。千兆以太网可以提供快速、灵活的通信,但以太网通信比简单的RS-232串口通信要稍微复杂一些。然而一旦你理解了这个概念,那其实也没有什么好担心的,在看完这个系列接下来的几篇博客文章后,我觉得你会掌握理解这个概念。

在Zynq SoC上的PS(控制系统)中有两个千兆以太网控制器。每个控制器都是可配置的,并且可以单独控制。千兆以太网控制器一旦被正确配置,可以实现一个MAC——介质访问控制层——7层OSI模型中数据链路层的组成之一。MAC构成OSI模型数据链路层的一小部分。在本系列接下来的几篇博客中,首先我们会深入研究MAC,然后进阶到TCP/IP及更高的协议层。因此,我认为有必要先简要回顾一下OSI系统模型。

开放式系统互联(OSI)7层模型使用一个抽象的模型来描述协议如何作用在协议栈中的不同层上。

1. 第一层:物理层——描述物理连接

2. 第二层:数据链路层——描述物理层上(物理地址)数据传输的途径。

3. 第三层:网络层——描述不同网络间(逻辑地址)数据传输的途径。

4. 第四层:传输层——提供终端用户间的数据传输

5. 第五层:会话层——控制终端用户间的连接

6. 第六层:表示层——在更高层和较低层间进行数据表示的传输

7. 第七层:应用层——最终数据被使用或聚集到另一个节点的接口

当然并不是说必须在每个层上都要求有协议的具体实现。

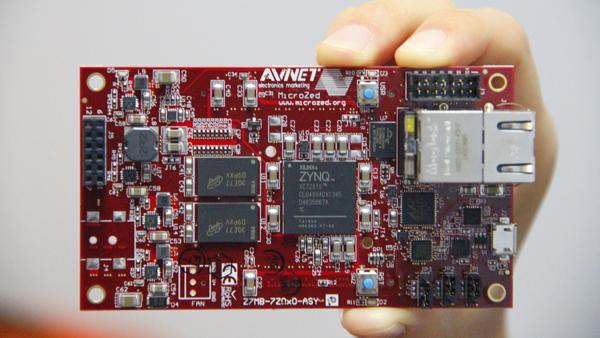

物理层用一个外部物理层设备实现。Zynq SoC使用两种方法的其中之一来和物理层设备接口,取决于你的系统设计。第一种选择是使用RGMII接口来把物理层设备连接到Zynq SoC的MIO上去。第二种方法是通过一个GMII/MII接口使用EMIO来把Zynq SoC连接到物理层设备上去。在MicroZed开发板上,具体物理层设备是一个连接到RJ45/USB连接器上去的Marvel Alaska 88E1512设备。

为了确保在最大连接数时可能使用PHY设备以及保证二次设计使用,已经开发出了一个被称为介质无关接口的标准接口,即上面RGMII、GMII和MII中的“MII”。“RG”的意思是“精简吉比特”,其中“G”是“吉比特”的简写。在较高数据速率或者信号管脚较少的情况下,MII标准会有相应的改变。

在研究过Zynq千兆以太网控制器如何接口到网络和外部世界后,我们现在将要来探索Zynq SoC上的内置以太网控制器如何同处理器系统接口。可以用一个简单的寄存器接口来提供控制和状态位,而双向千兆数据通信的高速传输则需在系统内存和以太网控制器间有一个DMA(直接内存访问)。

下面的几篇博客中,我们会借助几个赛灵思范例来研究MAC的配置。接着我们就可以去搭建更多可联网的设计了。

现在,你可以方便地获取第一年的亚当·泰勒MicroZed开发板编年史Kindle电子书版本了,很实惠仅需7.5美元。点击这里。

原文链接:

http://forums.xilinx.com/t5/Xcell-Daily-Blog/Adam-Taylor-s-MicroZed-Chro...

© Copyright 2014 Xilinx Inc

如需转载,请注明出处