By Adam Taylor

在先前的几篇博文中我们介绍了Zynq SoC上的千兆以太网控制器,其提供了介质访问控制层(MAC)功能。这是搭建一个IP栈的第一步。现在借助几个赛灵思SDK中提供的范例,我们将研究如何配置MAC来发送和接收数据包,该SDK显示了MAC具体是如何工作的。

首先,打开SDK然后参考带有千兆以太网控制的BSP来创建一个空白应用。(上述工作需要在Vivado设计套件中完成)

赛灵思SDK中有展示以太网MAC发送帧数据的完整范例。我将围绕这个不错的实例来阐述本部分。然而,要遵循要事第一的原则。首先我们需要在我们的工程中包含这些示例文件。通过几个简单的点击操作我们就能完成这个工作,选择导入->文件系统,定位到

<安装目录>

/SDK/2014.1/data/embeddedsw/XilinxProcessorIPLib/drivers/emacps_v2_0/examples

然后导入下列文件:

• c文件——例程本身文件

• c源文件——例程中所使用函数的具体实现

• h头文件——所使用函数的声明

把这些文件包含到你的工程中去之后,你就可以build示例工程了,如果板子和终端程序连上了,你应该可以看到示例成功(没连上则会失败)的现象。然而,上面这些步骤并不会帮助我们理解如何配置和使用Zynq SoC上的以太网MAC。

那么让我们来研究研究这些例程文件,然后看看它们具体如何工作,这样才能更好的理解MAC。我们从xemacps_example_intr_dam.c文件开始。该文件中第一步做的工作是:

1. 在进行相关声明后,该文件定义了一系列Rx和Tx缓冲器描述器、设备ID号、中断号和寄存器偏移和值。

2. 给发送和接收以太网数据帧声明全局变量,设置帧长度以及发送和接收的帧数目。

主要功能在函数EmacPSIntrExample中实现。该函数解锁SLCR(系统层控制寄存器),然后给MAC建立时钟,接着使用许多其它外设中用到的方式来配置和初始化MAC——查找配置,接着利用实例的指针来进行初始化。

初始化过后,MAC地址就设置好了。该地址包含在文件xemacps_example_util.c中,长度为6字节。其被定义为一个字符数组;本例中为00:0A:35:01:02:03。MAC地址是辨认连接到网络上节点的唯一标识。MAC地址设置好之后,有三个处理函数被创建,在发送、接收或错误发生的时候会调用它们。

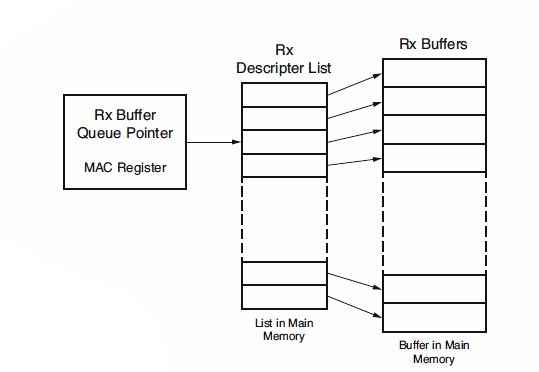

MAC配置完成之后,下一步就是给发送和接收缓冲器建立DMA缓冲器描述器(BD)了。

缓冲器描述器(BD)结构

XEmacPs_BdRingCreate(&(XEmacPs_GetRxRing

(EmacPsInstancePtr)),

RX_BD_LIST_START_ADDRESS,

RX_BD_LIST_START_ADDRESS,

XEMACPS_BD_ALIGNMENT,

RXBD_CNT);

要建立一个BD环,我们需要5样东西:

1. 接收或发送指针实例,本例中由函数XEmacPs_GetRxRing函数提供。对于发送也有相似的函数。

2. 缓冲区内存的物理起始地址——在先前的声明中定义

3. 缓冲区内存的虚拟起始地址——这里和物理地址相同,因为cache被禁用了。

4. 字节对齐方式,本例中为4字节对齐。

5. 所需创建缓冲区描述器的数量。

在创建好环之后,我们可以给新创建的环克隆一下缓冲区描述器模板。对于发送环也是进行类似的工作。

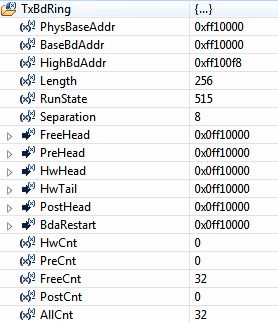

创建及克隆后的发送缓冲区描述器

函数EmacPsSetupIntrSystem使能中断。这和其它我们研究过的使用中断的例子很相似。(详情参见博客12和13)。

利用函数EmacPsDmaSingleFrameIntrExample可以产生和接收帧。该函数同时使用发送和接收缓冲区描述器来发送及接收1000字节有效负荷帧。在MAC配置为环回模式下,该函数仅仅是把发送帧和接收帧校验一下,以此来验证例程好使。

帧的构成是很有意思的。一个以太网帧的组成为:

8字节帧头

6字节目标地址

6字节源地址

2个类型字节——其定义了包含在数据填充里协议的类型

46到1500个数据或填充字节

4个CRC帧校验字节

发送帧TxFrame被定义为EthernerFrame类型。它是一个1532字符大小的字符数组。因此创建发送帧的方式是利用一个指向数组中每个成员的指针,然后把指针设置为需要的值。本例中,源地址及目标地址设置为和MAC地址一样。有效荷载仅仅包含了一个递增计数器的值,以太网类型设为1000。

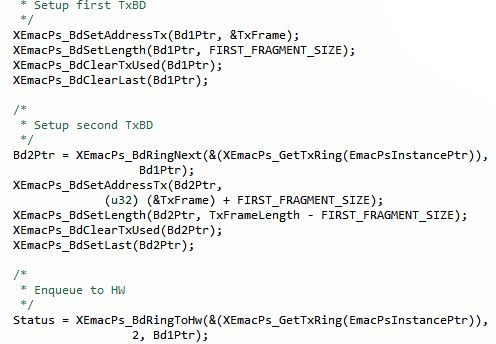

发送帧需要被插入到缓冲区描述器中去,这样我们才能把它提交到硬件。本例中,发送帧被分割到两个缓冲区描述器中去,以此来展示如何使用多重缓冲区描述器,而接收帧则包含在单缓冲区描述器中。

建立缓冲区描述器然后提交到硬件

接下来对于接收帧缓冲区描述器也是一样的过程,把它指向一个接收帧字符数组。在发送和接收帧缓冲区描述器都建立好并且提交到硬件之后,下面的描述就可以使能传输了:

传输完成后,处理函数被触发,发送帧计数器递增,然后缓冲区描述器被清空。接着会对比发送和接收帧来保证它们一致;成功或失败将会显示出来。

尽管花了很长时间解释所有的东西,然而如果想创建一个IP栈,我们必须理解MAC工作原理以及知道如何配置它。在经过这个例子后,我们可以看出配置Zynq SoC的以太网MAC来传输数据也没有什么难的。

现在,你可以方便地获取第一年的亚当·泰勒MicroZed开发板编年史Kindle电子书版本了,很实惠仅需7.5美元。点击这里。

原文链接:

http://forums.xilinx.com/t5/Xcell-Daily-Blog/Adam-Taylor-s-MicroZed-Chro...

© Copyright 2014 Xilinx Inc

如需转载,请注明出处

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网