作者:Steve Leibson, 赛灵思战略营销与业务规划总监

典型的嵌入式视觉系统必须处理视频帧,从这些处理的帧中提取特性,然后根据所提取的特性来决定下一步的动作。在你谈论高清或4K2K视频时,基于像 素的任务中每个像素可能需要数百个操作,并且需要数百个GOPS(千兆运算/秒)。 相比之下,基于帧的任务,每秒“仅”需要百万次的操作,但是算法更加复杂。你需要一个硬件实现像素级任务,同时快速处理器能够处理更复杂的“基于帧”的任 务。

Avnet的技术营销工程师Mario Bergeron在上周美国加州圣克拉拉举办的嵌入式视觉峰会2015 上对此做了一个演讲。

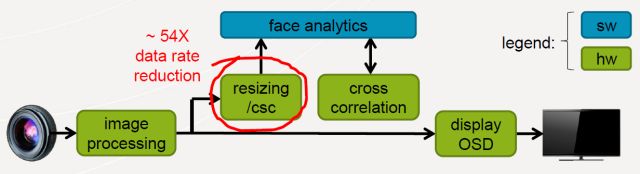

Bergeron演示了一个脸部识别和视线跟踪应用的幻灯片,其通过采用针对赛灵思全可编程器件的Xylon公司 LogicBricks IP实现的, 他还展示了系统如何分配硬件和软件之间的应用任务,如下图所示。

一个重要的因素要注意:在将其发送到微处理器之前,硬件减少了54x的图像数据率。

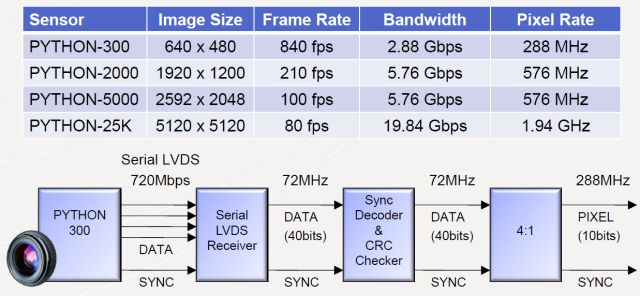

在Bergeron 演讲中提到的一个最有趣的点是嵌入式视觉设计者所必须要处理的范围广泛的接口。Bergeron展示了一个安森美半导体的PYTHON图像传感器系列中4 个图像传感器的幻灯片。传感器系列包括了这类器件,其图像大小范围从640x480像素 到5120x5120像素,帧速率范围从80到840帧/秒,和多个LVDS I/ O引脚的带宽要求范围从2.88到19.84Gbps。 制作一个可以处理这类图像传感器系列中所有传感器的硬件是很难的,但是交由赛灵思全可编程器件联合 XYLON 和 Auviz Systems厂商的现成IP核来处理就会很容易。

Bergeron 提到的另一个工具是针对赛灵思Zynq SoCs 和MPSoCs

的全新SDSoC开发环境,该开发环境提供了以软件为中心,系统级优化的编译器,其可以接受使用C或C++编写的系统描述,同时能自动生成实现所描述系统

所需要的软件应用和硬件配置。该SDSoC开发环境采用软件编译器、HLS(高层次综合)和预设的硬件基础设施来搭建这样的系统。

当天晚些时候,Bergeron在与嵌入式视觉峰会相连的展览会上的Avnet平台中展示了上述描述的应用。演示展示了实时运行在赛灵思Zynq SoC上的脸部识别应用,在MicroZed SOM (系统模块)上插入了一个特别的载卡。同时, MicroZed SOM和载卡构成Avnet嵌入式视觉开发套件,它可以接受来自多个供应商的图像。

该套件以及Xylon面部识别与视线追踪IP在3月份的VisionChina 2015展会上也有展示,以下是视频演示:

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网