问题

顶层模块有一个50MHz时钟输入(使用testbench实现);一个8位信号输出。

有一个容量为90的8位RAM子模块,每个时钟上升沿,RAM根据8位地址线,输出对应的数据。

顶层模块在每100个时钟周期里,前10个时钟周期信号无效,输出为0;后面90个时钟周期,输出值分别为RAM中地址0~89的数据。

代码实现

RAM子模块

module ram(input clk,input [7:0] addr,output reg [7:0] data);always @(posedge clk) begindata <= addr;endendmodule

顶层模块

module sync_async();// 50MHz时钟 testbenchreg clk = 0;always #10 clk = ~clk;// 0~99循环计数器reg [7:0] cnt = 0;always @(posedge clk) beginif(cnt == 99)cnt <= 0;elsecnt <= cnt + 1;end// 数据有效wire valid;assign valid = cnt >= 10;// 地址线wire [7:0] addr;assign addr = cnt - 10;// 调用子模块,读取ram数据wire [7:0] ramdata;ram ram1(clk, addr, ramdata);// 输出wire [7:0] out;assign out = valid ? ramdata : 0;endmodule

仿真与分析

一眼看上去,好像程序是没有问题的。

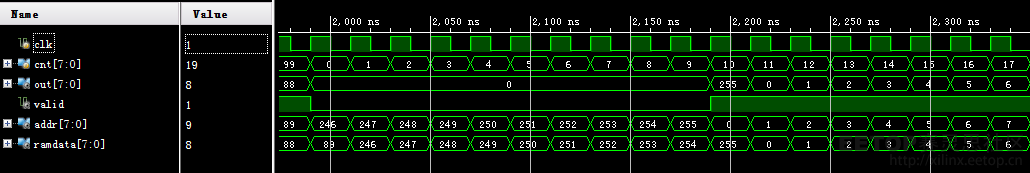

使用软件进行仿真后的时序图如下。

从仿真波形就看出问题来了。当cnt=0~9的时候,输出都是out=0没有问题。但是当cnt=10的时候,输出变成了255。之后所有的数据都滞后了一个时钟周期。

原因在于代码中的同步异步设计不协调。

代码中,RAM子模块是上升沿触发并且同步输出的(这样也比较符合正常的RAM结构),而不是直接由组合逻辑电路实现。如果直接将assign addr = cnt - 10作为RAM的地址线,RAM的输出相对于addr和cnt的值会滞后一个周期。也就是说,当RAM输出地址为0的数据时,实际上addr的值已经是1了。

在RAM模块的always语句中(

always @(posedge clk) data <= addr;),使用同步赋值操作data <= addr在时钟上升沿时触发,上升沿结束后data输出的值,为上升沿前一瞬间addr的值。

而另一方面,valid变量却使用的是直接异步赋值,相比cnt,不会有滞后。

于是在cnt==10的时候,valid已经变成1,而RAM还没有输出地址为0的数据,所以发生了与设计不相符的问题。

解决方法

一种比较容易想到的方法是,将valid信号的跳变,也设计成和RAM一样的上升沿同步触发。即将

// 数据有效wire valid;assign valid = cnt >= 10;

改为

// 数据有效reg valid = 0;always @(posedge clk) beginvalid = cnt >= 10;end

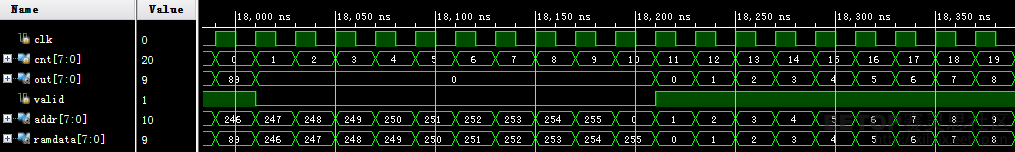

修改正确后的仿真波形如下图,可以看出valid信号和RAM信号相对于cnt,都滞后了一个周期。从而实现了问题中给出的要求。