Intel 4790K的主频是4.0GHz,高通801的单核频率可达2.5GHz,A8处理器在1.2GHz,MSP430可以工作在几十MHz……这里的频率的意思都是类似的,这些处理器的频率都是厂商给定的。但是对于FPGA的工作频率而言却往往需要我们自己决定,在产品的设计初始就需要考虑FPGA工作在哪个频率,譬如250MHz。这个取值并不是瞎确定的,譬如如果定在1GHz,那显然是不可能的,有一本叫《XXXXX FPGA Data Sheet DC and Switch Characteristics》的手册给出了FPGA各个模块的直流供电特性和最高工作频率。这里给出的是理论工作上限制,Virtex-5各个模块工作频率最高大概在400-500MHz之间。当然还要考虑FPGA的输入clk了,即使有DCM等模块分频倍频,一般也不会选择一个很奇怪的分频比。

一旦工作频率确定下来之后,问题就来了。你所建立的工程是否能在这一要求的工作频率下正常工作?只需要在UCF文件内添加时钟的周期约束,Place & Route之后就可以得到结果了。约束满足了,很好;没有满足,可以改,如何修改将在Achieving Timing Closure中介绍。

谈到这里,有一个问题呼之欲出:除了器件本身的限制,还有什么会影响工作频率?下文将介绍相关概念。

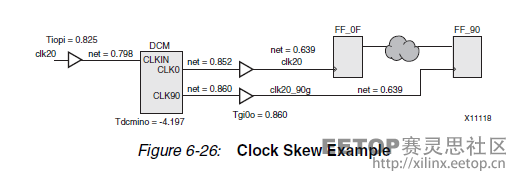

考虑同步时序电路中的触发器,在时钟沿到达的时候,数据必须是稳定(非亚稳态)且有效的(符合设计需求)。同步时序电路中,对于两个相连的触发器(譬如下图,Figure6-26),我们自然希望这两个触发器的时钟相位完全一致,但这往往是不现实的。不同的延时将破坏这一关系,延时差称为Clock Skew,即时钟歪斜。

Clock Skew = clock path delay to the destination synchronous element - clock path delay to te source synchronous element.

时钟的不同路径延时将破坏其原本完美的相位关系。但并不是说Clock Skew的取值为0是最好的 。Clock Skew是如何影响时钟周期(频率)将在第三节介绍。

注意,clock skew中只提到了path delay,但是实际上对于destination synchronous element 和source synchronous element而言,时钟的相位可能是不一样的。这一点表现出了时钟的相位和clock skew是独立的两个概念。在前文的OFFSET中,相位的表现为clock arrival time。

上图是一个clock skew的例子,可以看到两个触发器的时钟不是同相的,但是计算clock skew的时候没有必要考虑。以DCM的输出作为参考,源同步元素的路径延时为0.852+0.860+0.639 = 2.351,目的同步元素的路径时延为0.860 + 0.860 + 0.639 = 2.359。故clock skew = 0.008 。

Clock Uncertainty 的概念比较好理解,就是时钟的不确定性。时钟不确定性是时钟本身的不完美导致的。譬如对于100MHz时钟,上升沿本应该在0ns,10ns,20ns;实际上却在0ns,10.01ns,19.99ns,这个差距就是时钟的不确定性。时钟不确定性受到了多个因素的影响,其中一个因素是clock jitter,关于clock jitter,PERIOD约束中有一个INPUT JITTER的关键字告诉综合工具输入时钟的jitter。譬如

![clipboard[1] clipboard[1]](http://xilinx.eetop.cn/uploadfile/2015/08/3_2015081915383128Ic3.png)

不同情况下,Clock Uncertainty 的计算方式是不一样的,譬如DCM时钟下

Clock Uncertainty = [√(INPUT_JITTER² + SYSTEM_JITTER²) + DCM_Discrete_Jitter]/2 + DCM_Phase_Error

SYSTEM JITTER定义了整个系统的jitter,受到了电源噪声、板级噪声和系统任何外部jitter的影响。对于clock uncertainty和clock jitter来说,好像并没有什么太值得注意的地方。

Clock Domains

对于同步时序电路来说,不可避免的有时钟的存在,比较简单的就是所有的触发器都采用了一个时钟。那么可以认为整个设计中的路径都处于这个时钟的覆盖下,如下图,这两个触发器之间的路径是受到这一个时钟的时钟周期约束的。这种情况称为single clock domain。

![clipboard[2] clipboard[2]](http://xilinx.eetop.cn/uploadfile/2015/08/3_201508191538313Fo3E.png)

但是对于大多数设计来说,情况并不是这样的,譬如DCM可以分出不同相位的时钟。如下图,此时两个触发器的时钟不是一样的,而这两个触发器之间的数据路径连接了这两个时钟。什么是时钟域?域即是区域,时钟的区域,在我看来就是时钟覆盖的范围。下图中触发器之间的路径,一端属于clk20,一端属于clk20_90g,横跨了两个时钟域。注意这两个时钟是一个DCM产生的,时钟相关,因此XST能够对其进行分析。本节内容不谈跨时钟域的问题。

![clipboard[3] clipboard[3]](http://xilinx.eetop.cn/uploadfile/2015/08/3_2015081915383148jhu.png)

举例

以上图(Figure6-6)为例,计算slack。Requirement取决于两个触发器时钟的相对相位关系。注意到第一个触发器在下降沿采样,第二个触发器相移为90,时钟周期为20ns。结合前文的setup和OFFSET提及的相关概念。这是很好理解的。和OFFSET约束不同的是,OFFSET主要是受到外部信号的相对关系影响,Period则基本取决于设计。通过分析可知,限制最小时钟周期的影响因素在于data path。data path包括了布线延时和逻辑延时。了解到这一点,对之后代码编写是由帮助的。譬如,不能有太复杂的逻辑。(这是因为FPGA的LUT结构输入有限,以4输入为例,逻辑复杂需要LUT级联,那么自然会影响到逻辑延时)

Slack (setup path): 13.292ns (requirement - (data path - clock path skew + uncertainty))

Source: IntC_2 (FF)

Destination: XorB_2 (FF)

Requirement: 15.000ns

Data Path Delay: 2.594ns (Levels of Logic = 1)

Clock Path Skew: -0.086ns

Source Clock: clk0 falling at 10.000ns

Destination Clock: clk90 rising at 25.000ns

Clock Uncertainty: 0.200ns

周期约束分析

结合三节内容来看,注意式子Slack = requirement - (data path - clock path skew + uncertainty)) 。requirement是由时钟周期确定的,要判断时钟的周期约束是否得到满足,计算data path - clock path skew + uncertainty是否大于requirement 即可。data path是数据路径延时,另两个参数已经在1,2节介绍。

出处(http://www.cnblogs.com/sea-wind/)

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网