让XDC时序约束为您效力

发布者:jackzhang

时间:2016-01-21 16:02:11

作者:Adam Taylor e2v 公司首席工程师

时序和布局约束是实现设计要求的关键因素。本文是介绍其使用方法的入门读物。

完成 RTL 设计只是 FPGA 设计量产准备工作中的一部分。接下来的挑战是确保设计满足芯片内的时序和性能要求。为此,您经常需要定义时序和布局约束。

我们了解一下在基于赛灵思 FPGA 和 SoC 设计系统时如何创建和使用这两种约束。

时序约束最基本的时序约束定义了系统时钟的工作频率。然而,更高级的约束能建立时钟路径之间的关系。工程师利用这类约束确定是否有必要对路径进行分析,或者在时钟路径之间不存在有效的时序关系时忽视路径。

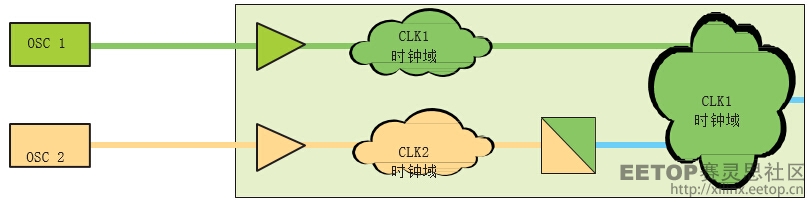

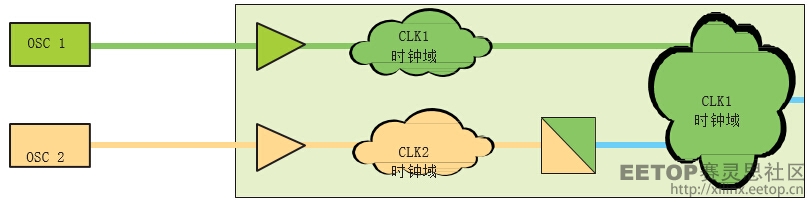

默认情况下,赛灵思的 Vivado? 设计套件会分析所有关系。然而,并非设计中的所有时钟之间都有可以准确分析的时序关系。例如当时钟是异步的,就无法准确确定它们的相位,如图 1 所示。

图 1–时钟域 CLK1 和 CLK2 相互之间异步。

您可通过在约束文件中声明时钟组来管理时钟路径之间的关系。当声明时钟组时,Vivado 工具不会对组内定义的时钟之间的任何方向执行时序分析。

为了有助于生成时序约束,Vivado 工具将时钟定义为三种类型:同步、异步或不可扩展。

- 同步时钟具有可预测的时序/相位关系。通常主时钟及其衍生时钟符合这种特性,因为它们具有公共的根起源和周期。

- 异步时钟之间不具备可预测的时序/相位关系。通常不同的主时钟(及其衍生时钟)符合这种特性。异步时钟有不同的起源。

- 如果超过1,000个周期后,仍无法确定公共周期,那么两个时钟就是不可扩展的。如果是这种情况,将使用 1,000 个周期内的最差建立时间关系。不过,无法保证这就是实际的最差情况。

使用 Vivado 生成的时钟报告来确定您所处理的时钟是哪种类型。该报告可帮助您识别异步和不可扩展时钟。

识别出这些时钟后,您就可利用“set clock group”约束禁止它们之间的时序分析。Vivado 套件使用的是赛灵思设计约束 (XDC),其基于广泛使用的 Tcl 约束格式的 Synopsys 设计约束 (SDC)。通过 XDC 约束,您可使用以下命令定义时钟组:

set_clock_groups -name -logically_exclusive -physically_exclusive -asynchronous -group -name 是为组赋予的名称。-group 选项是定义组成员(即没有时序关系的时钟)的位置。当有多个用来驱动时钟树的时钟源可供选择,包括 BUFGMUX 和 BUFGCTL,应使用 logically 和 physically exclusive 选项。从而,这些时钟不能同时出现在时钟树上。所以,我们不希望 Vivado 分析这些时钟之间的关系,因为它们是互斥的。最后,–asynchronous 约束可用来定义异步时钟路径。

建立时序关系的最后一个方面是考虑时钟的非理想关系,尤其是抖动。您需要考虑两种形式的抖动:输入抖动和系统抖动。输入抖动出现在主时钟输入上,体现了实际跳变出现时间与理想条件下跳变出现时间之间的差异。系统抖动源自设计中存在的噪声。

您可以使用 set_input_jitter 约束来定义每个主输入时钟的抖动。同时,使用 set_system_jitter 约束为整个设计(所有时钟)设定系统抖动。

时序例外当有时序例外时,您还必须关注已定义的时钟组内发生了什么。然而,什么是时序例外呢?

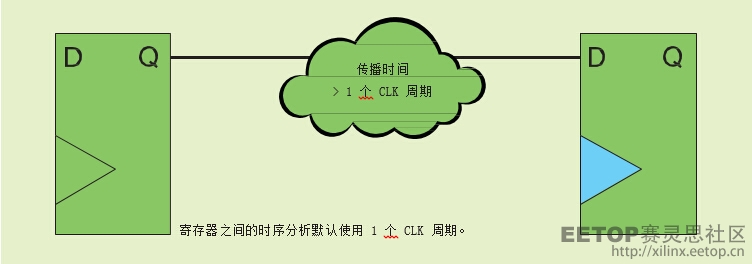

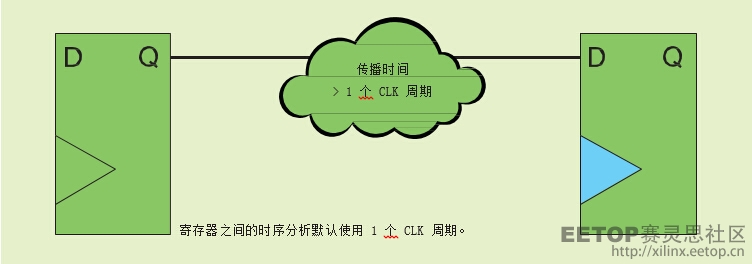

一种常见的时序例外是只有每隔一个时钟周期所采样的结果。另一种情况是将数据从慢时钟传输到更快的时钟(或相反),其中两个时钟都是同步的。事实上,这两种时序例外一般被称为多周期路径,如图 2 所示。

为这些路径声明多周期路径能实现更合适而且要求放松的时序分析,从而让时序引擎集中处理其它更关键的路径。最后的益处是能够提高结果质量。

您可以在 XDC 文件中使用以下 XDC 命令声明多周期路径:

图 2–多周期路径是一种时序例外的例子。

set_multicycle_path path_ multiplier [-setup|-hold][-start|-end][-from <start- points>] [-to <endpoints>][-through <pins|cells|nets>]

当您声明多周期路径时,实际上是将建立或保持(或二者皆有)分析要求与 path_mutiplier 相乘。例如在上面的第一个实例中,每两个时钟周期有一次输出,因此对于建立时序而言 path_multiplier 是 2。由于多周期路径既可应用到建立时间又可应用到保持时间,那么您可以选择其应用位置。当您声明建立时间乘数时,最佳做法通常是使用下面的公式同时声明一个保持时间乘数。

保持周期 = 建立乘数 – 1 – 保持乘数

这对于我们所介绍的下列简单实例意味着,保持乘数由下面这个公式确定:

保持乘数 = 建立乘数 – 1,当使用公共时钟时。

为了演示多周期路径的重要性,我创建了一个简单实例,您可在这里下载。在 XDC 文件中有一个实例包含了建立和保持这两个已被同时声明的多周期路径。

物理约束最常用的物理约束是 I/O 引脚布局和与 I/O 引脚有关的参数定义,例如标准驱动强度。不过,还有其它类型的物理约束,包括布局、布线、I/O 和配置约束等。布局约束能够定义单元的位置,而布线约束可用来定义信号的布线。I/O 约束可用来定义 I/O 位置及其参数。最后,配置约束可用来定义配置方法。

同样,也有一些约束不属于这几组约束。Vivado 设计套件包含三种这样的约束,它们主要用于网表中。

- DONT_TOUCH – 该约束可用来阻止优化,这样当实现安全关键型或高可靠性系统时该约束会非常有用。

- MARK_DEBUG – 该约束可用来保存 RTL信号,以便随后用于调试。

- CLOCK_DEDICATED_ROUTE – 该约束可用来识别时钟布线。

最常用的约束与 I/O 布局和 I/O 的配置有关。将 I/O 放在 FPGA 上,需要使用布局约束找到物理引脚,使用 I/O 约束配置 I/O 标准和斜率等 I/O 属性。

现代化的 FPGA 支持多种单端和差分 I/O 标准。这些均可通过 I/O 约束来进行定义。不过,您必须确保遵守 I/O Banking 规则,这取决于最后的引脚布局。

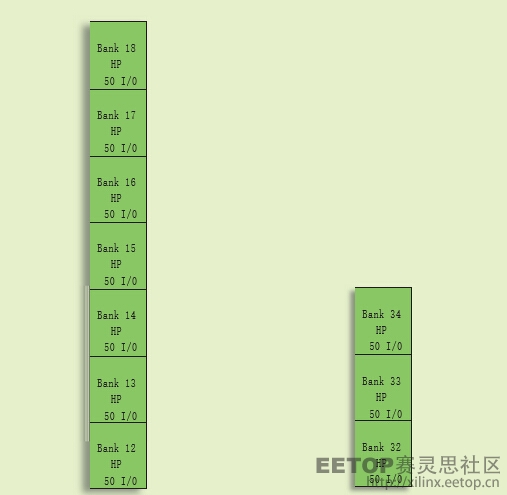

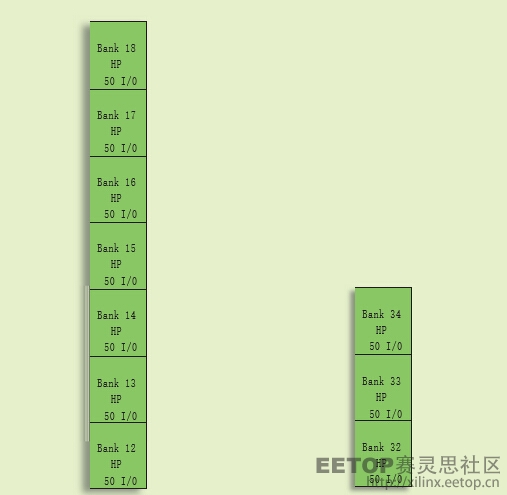

但什么是 I/O Banking 规则?将 FPGA 中的用户 I/O 分组为若干个 Bank,每个 Bank 包含多组 I/O。这些 Bank 具有独立的电压源,能支持多种 I/O 标准。在 Zynq?-7000 All Programmable SoC(以及其它 7 系列器件)中,I/O Bank 被进一步分为高性能和大范围这两个大的组别。这种类别划分能进一步约束性能,并要求工程师针对接口使用正确的类别。

高性能 (HP) 类别针对更高的数据速率进行了精心优化。它使用更低的工作电压,而且不支持 LVCMOS 3v3 和 2v5。另一个是大范围 (HR) 类别,其可处理 HP 不支持的更多 I/O 标准。因此,HR 支持传统的 3v3 和 2v5 接口。图 3 给出了这些 Bank。

当您决定为信号使用哪种 Bank 后,仍然可以更改信号驱动强度和斜率。这些都是硬件设计团队很感兴趣的指标,因为他们要努力确保单板的信号完整性达到最优。选择结果还会影响单板设计的时序。为此,您可以使用信号完整性工具。

SI 工具需要 IBIS 模型。当您打开了Impelmented Design时,您可使用 File->Export->Export IBIS 模型选项从 Vivado 工具中提取设计的 IBIS 模型。然后,使用该文件关闭解决系统级 SI 问题和最终 PCB 布局的时序分析。

如果设计团队整体上对 SI 性能以及系统的时序感到满意,

您就会得到针对设计中 I/O 的多个约束,如下所示。

set_property PACKAGE_PIN G17 [get_ports {dout}] set_property IOSTAN- DARD LVCMOS33 [get_ports{dout}]

set_property SLEW SLOW [get_ports {dout}]

set_property DRIVE 4 [get_ ports {dout}]

对于 HP I/O Bank,您还可使用数控阻抗正确做IO端接并增加系统的 SI,无需使用外部端接方案。如果没有信号驱动 I/O,例如将 I/O 连接到外部

连接器,这时您还必须考虑 I/O 的影响。这种情况下,您可使用 I/O 约束实现上拉或下拉电阻,以防止由于 FPGA 输入信号悬置而导致系统问题。

当然,您也可以使用物理约束在 I/O block 内放置最终的输出触发器,以改善设计的时序。这样做能缩短clock to out的时间。您也可以对输入信号做相同的处理,以使设计满足引脚到引脚的建立和保持时间要求。

物理约束从布局开始您可能出于多种原因想对布局进行约束,例如帮助达到时序要求,或者在设计的不同区域间实现隔离。就此而言,有三种类型的约束很重要:

- BEL –将网表单元放在 slice 中的基本的逻辑元素。

- LOC –将网表的单元放在器件内的一个位置。

- PBlock – 可使用物理(或“P”)block 将逻辑 block 约束到 FPGA 的一个区域。

因此,LOC 允许在器件内定义一个 slice 或其它位置;BEL 约束可用来定义触发器在 slice 中使用的更精细粒度。当对设计的大面积区域进行分段时,PBlock 可用来将逻辑集合在一起。PBlock 的另一个用途是在执行部分重配置时定义逻辑区域。

有些情况下,您需要将较小的逻辑功能放在一组,以确保时序达到最佳。尽管可以用 PBlock 来实现,但更常见的方法是使用相对放置的宏命令。

相对放置的宏命令(RPM)允许将 DSP、触发器、LUT 和 RAM 等设计元素在布局中放在一起。

图 3 – 赛灵思 7 系列器件上的高性能(左)和大范围 I/O Bank

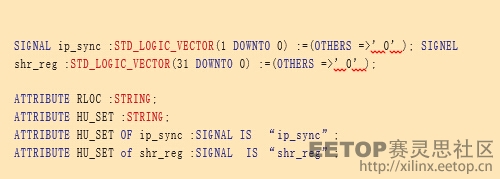

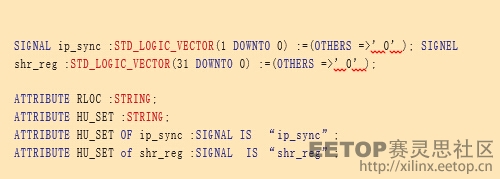

图 4 – 源代码中的约束

与 PBlock 不同,RPM 不会将这些元素的位置约束在器件的特定区域(除非您想这样做),而是在布局时将这些元素放在一起。

将设计元素放在一起能实现两个目标。这样能改善资源效率,让您能够精细调节互联长度,以实现更好的时序性能。

要将设计元素放在一起,可使用三种类型的约束,这些约束用 HDL 源文件进行定义。

- U_SET 可定义一个与层级无关的单元 RPM 集。

- HU_SET 可定义有层级的单元 RPM 集。

- RLOC给定义好的SET分配相对位置。

RLOC 约束被定义为 RLOC = XmYm,其中 X 和 Y 与 FPGA 阵列的坐标有关。当定义 RLOC 时,既可以用相对坐标也可以用绝对坐标,取决于您是否添加了 RPM_GRID 属性。添加这个属性后,该定义将成为绝对坐标而非相对的。由于这些约束在 HDL 中定义,如图 4 所示,因此在将约束添加到 HDL 文件之前,通常需要首先运行布局布线设计反复,以便正确定义布局。

总之,理解时序和布局约束并学习如何正确使用它们,对于在赛灵思可编程逻辑设计中获得最佳结果质量至关重要。