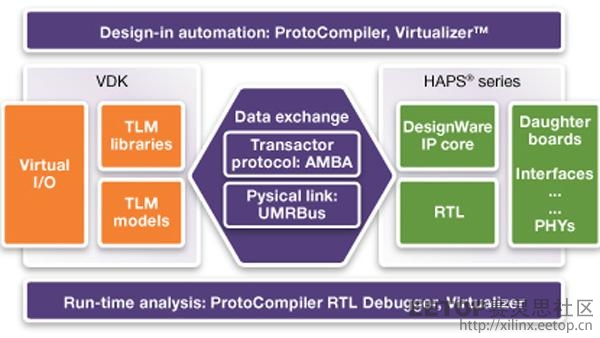

如今,设计人员使用两种相对独立的方法进行 SoC 原型验证:以事务级模型为基础的虚拟原型验证和基于 FPGA 的原型验证。 虚拟原型验证执行快速的 TLM,并可提供更高效的调试和分析方案,非常适合加速 RTI 前的软件开发。 基于 FPGA 的原型设计,提供精确的周期、较高的执行效率和连接到外部的实际接口。 Synopsys 的混合原型解决方案将虚拟原型和基于 FPGA 的原型优势集于一身,加速了项目周期中软件开发和系统集成的进度。

借助 Synopsys 的混合原型验证解决方案,硬件和软件工程师可:

1、无缝连接虚拟原型和基于 FPGA 的原型,通过混合原型达到两全其美的效果

2、更早地开始多核 SoC 原型验证,利用直接连接的实际硬件接口,提高系统级模型的执行效率

3、在虚拟原型和基于 FPGA 的原型环境间划分 SoC 设计模块,从而优化整体原型性能

4、通过基于 Virtualizer 的环境提高调试的可视性,加强对所开发软件的控制

5、通过对新的设计模块使用虚拟原型,以及对现存逻辑模块使用基于 FPGA 的原型,加快系统的启动

6、轻松地将高性能 ARM® Cortex™ 处理器模型、ARM AMBA® 互联事务处理器和 Synopsys DesignWare® IP 与您的其他设计相集成,构成一个混合原型

在虚拟原型和基于FPGA的原型之间用于数据交换的事务处理器,在HAPS-80,HAPS-70和HAPS-DX上已经实现了。Protocompiler是一套综合的软件工具,它包含的库可以支持混合原型验证或基于事务的验证。

附件:点击下载手册

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网