作者:huxiaokai2005

原文:http://bbs.eetop.cn/thread-611624-1-1.html

以太网可以说是现今应用最广泛的数据通信协议之一,本篇从物理层对以太网在Artix-7 50T开发板上应用进行评测。

一、原理:

按照技术发展以太网可以分为:标准以太网、快速以太网、千兆以太网和万兆以太网。

标准以太网只有10Mbps的吞吐量,使用的是带有冲突检测的载波侦听多路访问的访问控制方法,使用粗同轴电缆、细同轴电缆、非屏蔽双绞线、屏蔽双绞线和光纤等多种传输介质进行连接,并且在IEEE 802.3标准中,为不同的传输介质制定了不同的物理层标准,如10Base-5,10Base-T,10Broad-36,10Base-F等,在这些标准中前面的数字表示传输速度,单位是“Mbps”,最后一个数字表示单段网线长度(基准单位是100m),Base表示“基带”的意思,Broad代表“宽带”;

快速以太网可以达到100Mbps的带宽,支持3、4、5类双绞线以及光纤的连接,不过仍是基于CSMA/CD技术,可分为100BASE-TX 、100BASE-FX、100BASE-T4三个子类;

千兆以太网技术作为最新的高速以太网技术,可达到1Gbps的吞吐量,给用户带来了提高核心网络的有效解决方案,这种解决方案的最大优点是继承了传统以太技术价格便宜的优点。千兆技术仍然是以太技术,它采用了与10M以太网相同的帧格式、帧结构、网络协议、全/半双工工作方式、流控模式以及布线系统。千兆以太网技术有两个标准:IEEE802.3z和IEEE802.3ab。IEEE802.3z制定了光纤和短程铜线连接方案的标准,IEEE802.3ab制定了五类双绞线上较长距离连接方案的标准。

万兆以太网规范包含在 IEEE 802.3 标准的补充标准 IEEE802.3ae中,它扩展了IEEE 802.3 协议和 MAC 规范,使其支持 10Gb/s 的传输速率。除此之外,通过 WAN 界面子层(WIS:WAN interface sublayer),10千兆位以太网也能被调整为较低的传输速率,如 9.584640 Gb/s (OC-192),这就允许10千兆位以太网设备与同步光纤网络(SONET) STS -192c 传输格式相兼容。

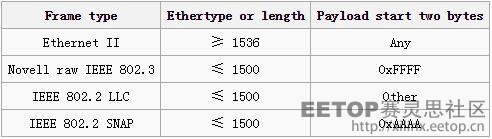

以太网数据传输以“帧”为基本单位,其中可分为四类:

1)Ethernet II

2)Novellraw IEEE 802.3

3)IEEE802.2 LLC

4)IEEE802.2 SNAP

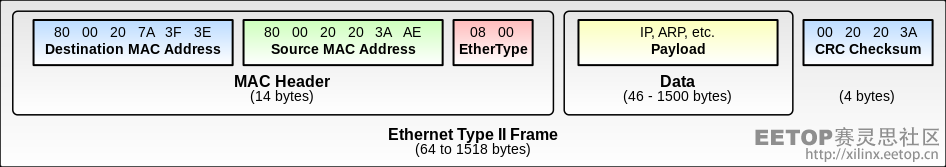

以EthernetII为例,如下图,一帧可分成:6bytes Destination MAC Address,6bytes Source MAC Address,2bytes EtherType,46~1500 bytes Payload和4bytes CRC Checksum。

不同的帧类别,其MTU(maximumtransmission unit)和格式会有不同,如下表

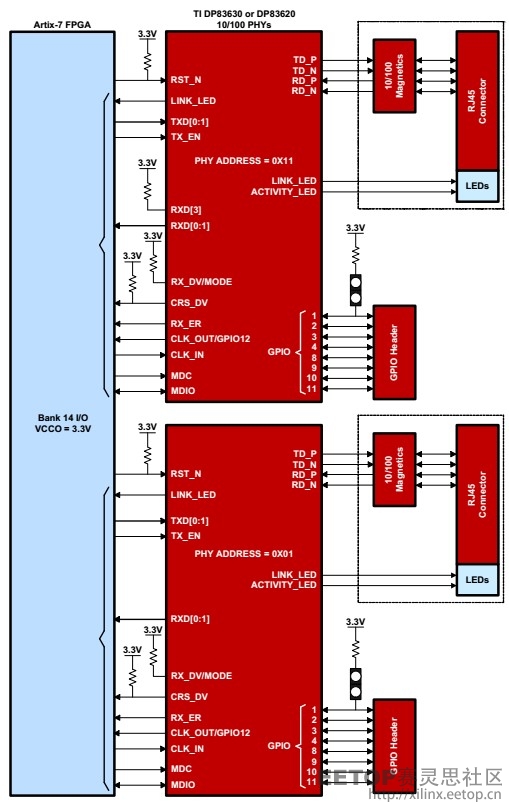

Artix-750T开发板上的以太网接口如下图所示,选用两片TITP83630以太网物理层传输芯片(PHY)。FPGA与PHY之间是RMII接口,RMII在保证传输吞吐量的情况下,相比于MII接口需要的引脚更少,FPGA内部通过MAC控制与PHY之前的数据传输;

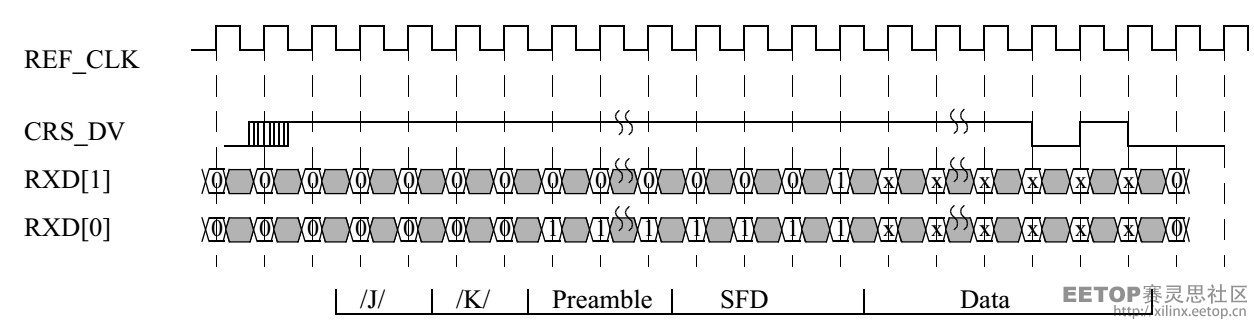

RMII接口共有8根信号:

l输入端:RX_ER,错误检测输入信号;CRS_DV,载波侦听/输入数据有效;RXD[1:0],输入数据

l输出端:TX_EN,输出有效;TXD[1:0],输出数据

l参考时钟:REF_CLK,50MHz,由FPGA输出给PHY

二、环境搭建:

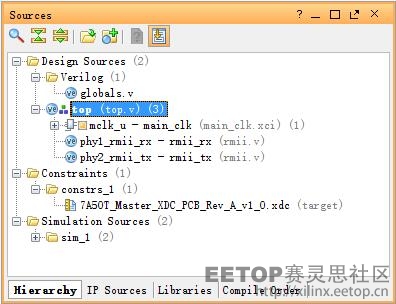

开始调试RMII接口,在Vivado中建立工程,编写代码,系统结构如下所示,PHY1接收数据 à

中间数据缓冲 à PHY2输出数据。

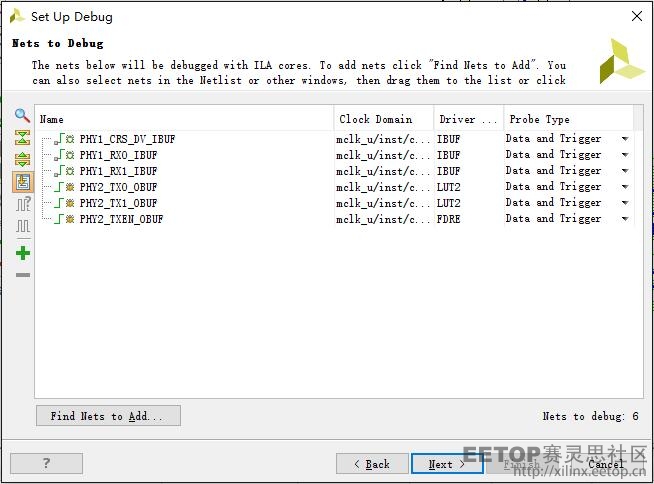

Run Synthesis后,通过Set Up Debug将RMII接口相关的信号加入到ILA cores中,以便后续调试。

进行后续进程:Run Implementation和Generate Bitstream完成vivado工程的搭建;然后进行硬件环境的搭建,如下图所示,两个以太网口分别通过USB网卡连接至PC,右侧用于将数据从PC发送到Artix-7 50T开发板,左侧用于在PC端接收来自Artix-7 50T开发板的数据。

三、调试:

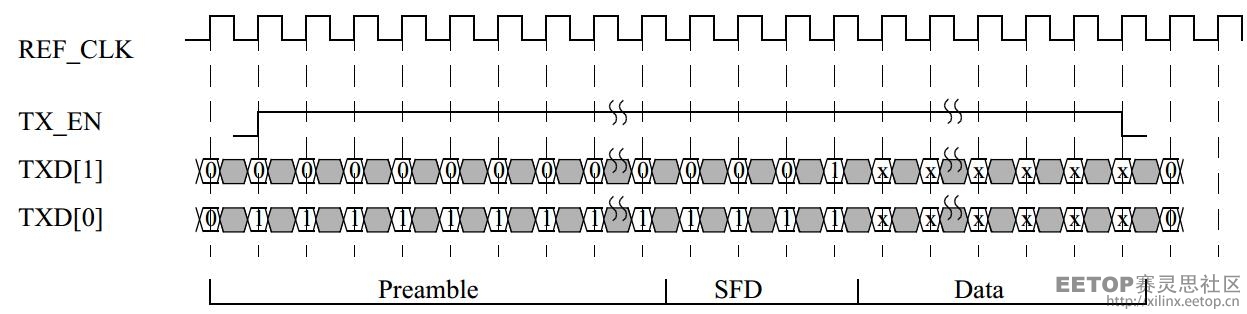

为了方便比对,如下图所示为RMII接口数据接收的时序图:

笔者在PC端调用WinPcap库写了个发送以太网帧的小程序

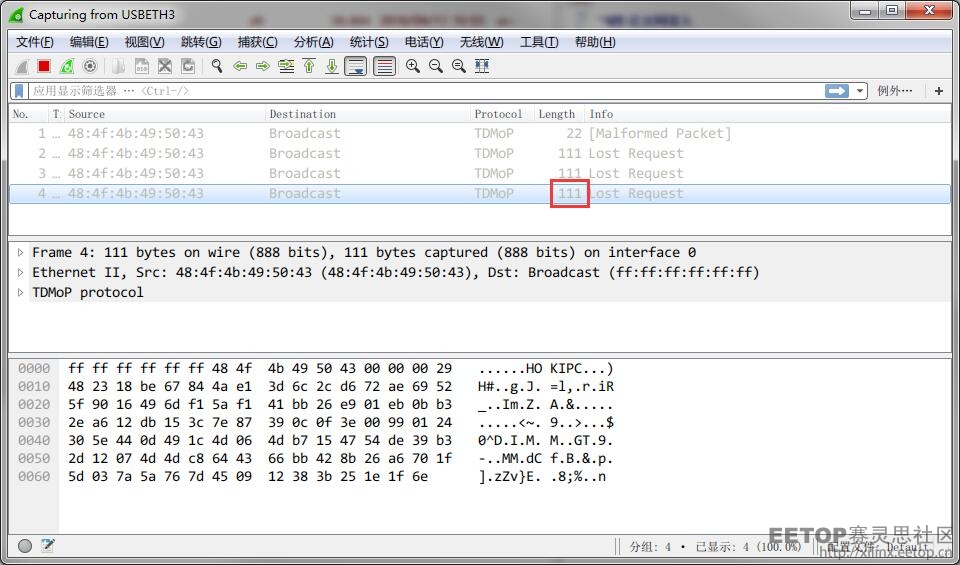

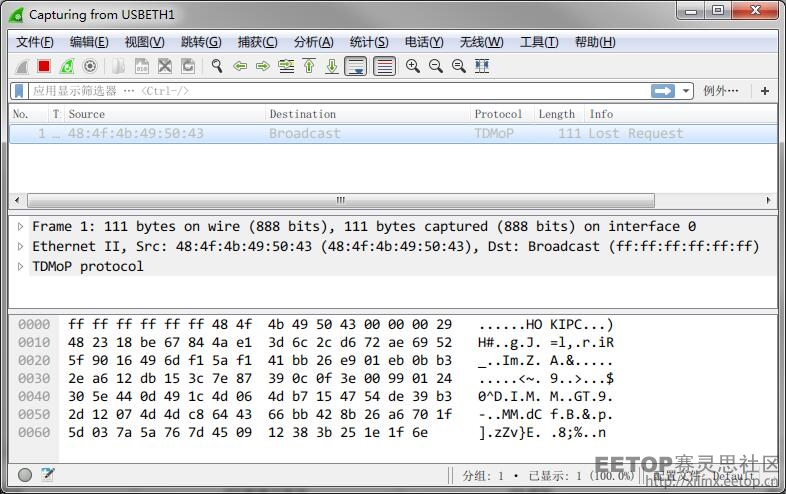

发送以太网帧的同时,使用Wireshark侦听右侧USB网卡,如下图为抓取的以太网数据包,大小为111字节。

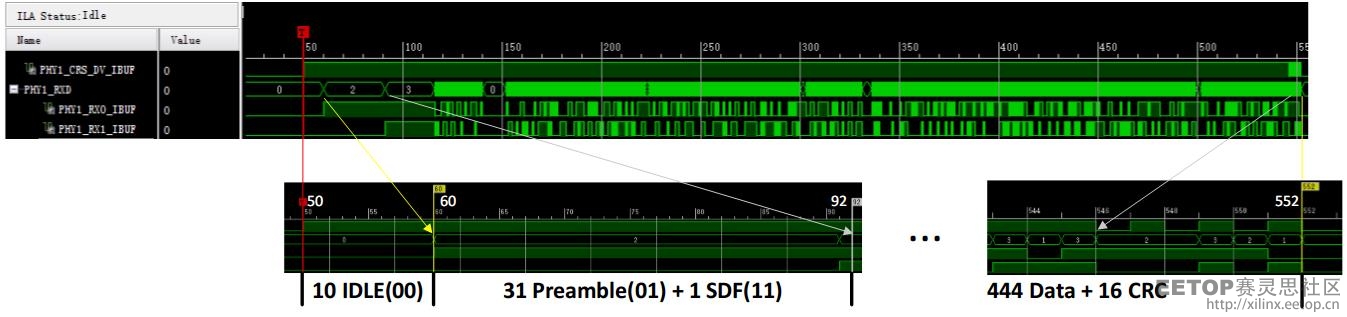

同时在Vivado设置CRS_DV的上升沿作为触发,如下图为抓取CRS_DV,RXD[1:0]的时序图,总共为502个时钟周期,减去10个时钟周期IDLE,32个时钟周期Preamble+SDF和16个时钟周期CRC,剩下444个时钟周期数据,其中每个时钟周期传输2比特数据,所以得到111字节,PC端发送和FPGA抓取的数据一致。

RMII接口发送数据的时序图如下

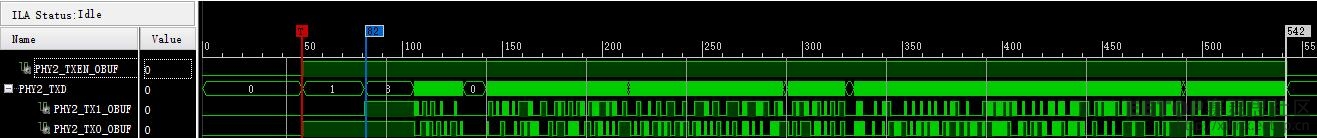

由PHY1接收到的数据,不经过处理,直接通过PHY2输出,Vivado抓取TX_EN,TXD[1:0]的时序如下图,总共492个时钟周期,减去32个时钟周期Preamble+SDF和16个时钟周期CRC,剩下444个时钟周期数据。

在Wireshark中侦听另一个USB网卡,如下图,接收到以太网帧,大小111字节,数据也与发送的数据一致。

如下动态图,两个网口的右侧LED灯会闪一下,说明有数据交互

四、总结

本篇评测首先介绍了以太网的基本知识,然后在Artix-7 50T上评测了以太网的物理层数据传输,调试了RMII接口的发送和接收时序,评测结果与理论一致。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网