2018年3月19日,北京 — 自适应和智能计算的全球领先企业赛灵思公司(Xilinx, Inc.,(NASDAQ:XLNX)),今天宣布推出一款 超越 FPGA 功能的突破性新型产品,名为ACAP(Adaptive Compute Acceleration Platform,自适应计算加速平台)。ACAP 是一个高度集成的多核异构计算平台,能根据各种应用与工作负载的需求从硬件层对其进行灵活修改。ACAP 可在工作过程中进行动态调节的自适应能力,实现了 CPU 与 GPU 所无法企及的性能与性能功耗比。

在大数据与人工智能迅速兴起的时代,ACAP 理想适用于加速广泛的应用,其中包括 视频转码、数据库、数据压缩、搜索、AI推断、基因组学、机器视觉、计算存储及网络加速等。软硬件开发人员将能够针对端点、边缘及云应用设计基于 ACAP 的产品。首款 ACAP 产品系列,将是采用台积电 7 纳米工艺技术开发的代号为“Everest(珠穆朗玛峰)”的产品系列,该产品将于今年年底实现流片。

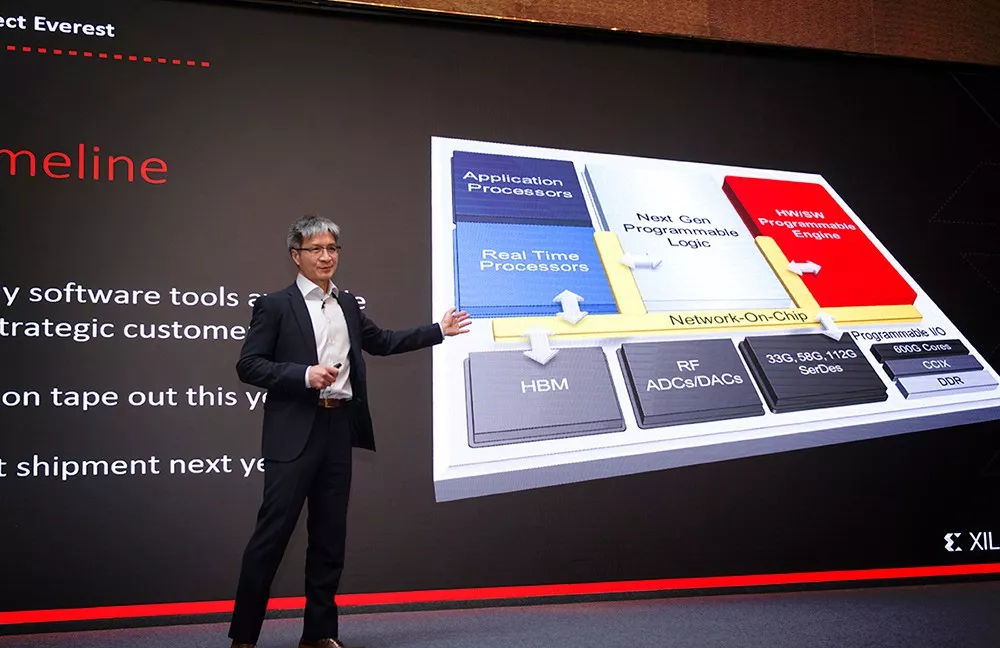

图1:Victor Peng 介绍 ACAP 可以给开发者带来的诸多好处

赛灵思总裁兼首席执行官(CEO)Victor Peng 表示:“这不仅对业界来说是一项重大的技术颠覆,更是我们自发明 FPGA 以来最卓著的工程成就。这款革命性的全新架构是赛灵思更广泛市场战略的一部分,将帮助公司朝着 FPGA 以外的领域发展,并突破‘仅支持硬件开发者’的局限。ACAP 产品在数据中心以及我们广泛市场领域的应用,将加速自适应计算技术的广泛普及,从而让智能、互连、自适应的世界更早成为现实。”

「

ACAP技术细节

自适应计算加速平台

」

ACAP 的核心是新一代的 FPGA 架构,结合了分布式存储器与硬件可编程的 DSP 模块、一个多核 SoC 以及一个或多个软件可编程且同时又具备硬件自适应性的计算引擎,并全部通过片上网络(NoC)实现互连。ACAP还拥有高度集成的可编程I/O功能,根据不同的器件型号这些功能从集成式硬件可编程存储器控制器,到先进的SerDes收发器技术,前沿的RF-ADC/DAC和集成式高带宽存储器(HBM)。

图2:Victor Peng 介绍 ACAP 的核心 — 新一代 FPGA 架构

软件开发人员将能够利用 C/C++、OpenCL 和 Python 等软件工具应用ACAP系统。同时,ACAP也仍然能利用 FPGA 工具从RTL 级进行编程。

“这就是未来计算的形式。我们所说的是能在几分钟内即完成基因组排序,而非几天;数据中心能根据计算需求自行对其服务器的工作负载进行编程调整,例如在白天进行视频转码,晚上则执行影像识别。这一点意义重大。”——Patrick Moorhead,Moor Insights & Strategy 市场调查公司创始人

ACAP历经四年的研发,累积研发投资逾 10 亿美元。赛灵思目前有超过 1500 名软硬件工程师参与“ACAP 和Everest”的设计。目前,软件工具已交付给主要客户。首款“Everest”产品将于 2018 年实现流片,于 2019 年交付给客户。

“Everest” 的性能提升

与当今最新的 16 纳米Virtex VU9P FPGA 相比,“Everest”有望将深度神经网络的性能提升20 倍!基于“Everest”的 5G 远程无线电头端和目前最新的 16 纳米无线电相比可将带宽提升 4 倍。届时,跨多个市场领域的各种应用都能实现性能和功耗效率的显著提升,这些市场包括汽车、工业、科学与医疗、航空航天、测试、测量与仿真、音视频与广播以及消费类电子产品市场等。

此次 ACAP 和 “Everest” 行动的发布,是Peng先生对Xilinx未来愿景的一部分。(详情请参见新闻稿: Xilinx CEO 描绘公司新愿景与战略蓝图)。如需了解更多信息,请访问 china.xilinx.com。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网