静态时序分析是学习FPGA必须学习的一个知识点,通过一段时间的学习,先将自己所学到的一点静态时序分析的基础稍作总结。

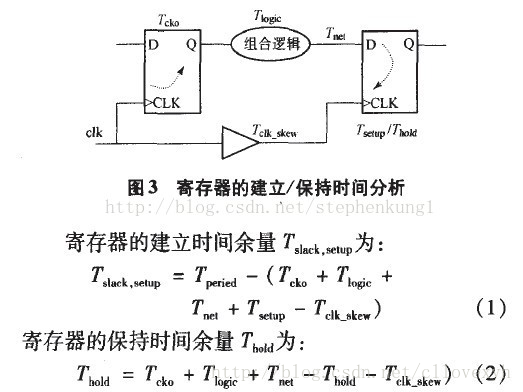

这是一张再熟悉不过的图形,以及两个基础公式

Tperiod>Tcko+Tlogic+Tnet+Tsetup-Tclk_skew (1)

Tcko+Tlogic+Tnet>Thold+Tclk_skew (2)

这里,为了得到更加简单的理解,忽略两项Tnet和Tclk_skew。原因在于Tnet通常太小,而Tclk_skew还牵扯到时钟uncertain,暂时可以不考虑skew的影响。简化后如下:

Tperiod>Tcko+Tlogic+Tsetup (3)

Tcko+Tlogic>Thold (4)

(3)式比较好理解,意思是数据从第一个触发器采样时刻传到第二个触发器采样时刻,不能超过一个时钟周期啊!假如数据传输超过一个时钟周期,那么就会导致第二个触发器开始采样的时候,想要的数据还没有传过来呢!对于(4)式两边同时加上Tsetup,得到(5)。

Tcko+Tlogic+Tsetup>Thold+Tsetup (5)

结合(3)式和(5)式,我们得到如下的式子:

Thold+Tsetup

Tcko+Tlogic+Tsetup是指数据从第一级触发器采样瞬间开始,传输到第二级触发器并被采样的传输延时。我们简称为数据传输延时。

下面讲述(6)式两端的含义。

Tcko+Tlogic+Tsetup< Tperiod

约定数据传输延时不能太大,如果太大(超过一个时钟周期),那么第二级触发器就会在采样的时刻发现数据还没有到来。

Thold+Tsetup

约定数据传输延时不能太小。Thold+Tsetup是一个触发器的采样窗口时间,D触发器并不是绝对的瞬间采样,它不可能那么理想。

在D触发器采样的瞬间,在这瞬间之前Tsetup时间之内,或者这瞬间之后Thold时间之内,如果输入端口发生变化,那么D触发器就会处于亚稳态。所以采样是有窗口的,我们把Thold+Tsetup的时间宽度叫做触发器的采样窗口,在窗口期内,D触发器是脆弱的,对毛刺没有免疫力的。假如数据传输延时特别小,那么下一级D触发器的保持时间就难以保证。

所以,数据传输延时既不能太大以至于超过一个时钟周期,也不能太小以至于小于触发器采样窗口的宽度。

本文转载自:CLGo的博客

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网