简介

这是学习SDSoc的第二个入门实验,通过EMIO点亮连接在PL上的8个LED。与上一个实验不一样,在这一个实验中,由于ZedBoard平台中没有使能EMIO,因此想直接通过SDSoc编写程序驱动MIO是不行的,所以这一个实验需要自己搭建包含EMIO的平台。

我用的是ZedBoard开发板,SDSoc2017.4。

第一步:搭建平台

通过对官方资料的学习,平台分为软件平台和硬件平台两部分,官方就如何搭建平台提供了较为详细的说明,可以在XILINX官网中搜索ug1146 和ug1236 两篇文档并下载。其中ug1146 理论讲解比较详细,ug1236 重在叙述操作实践,本实验需要搭建的平台就是参照这两篇文档,同时增加了一点点东西完成的。

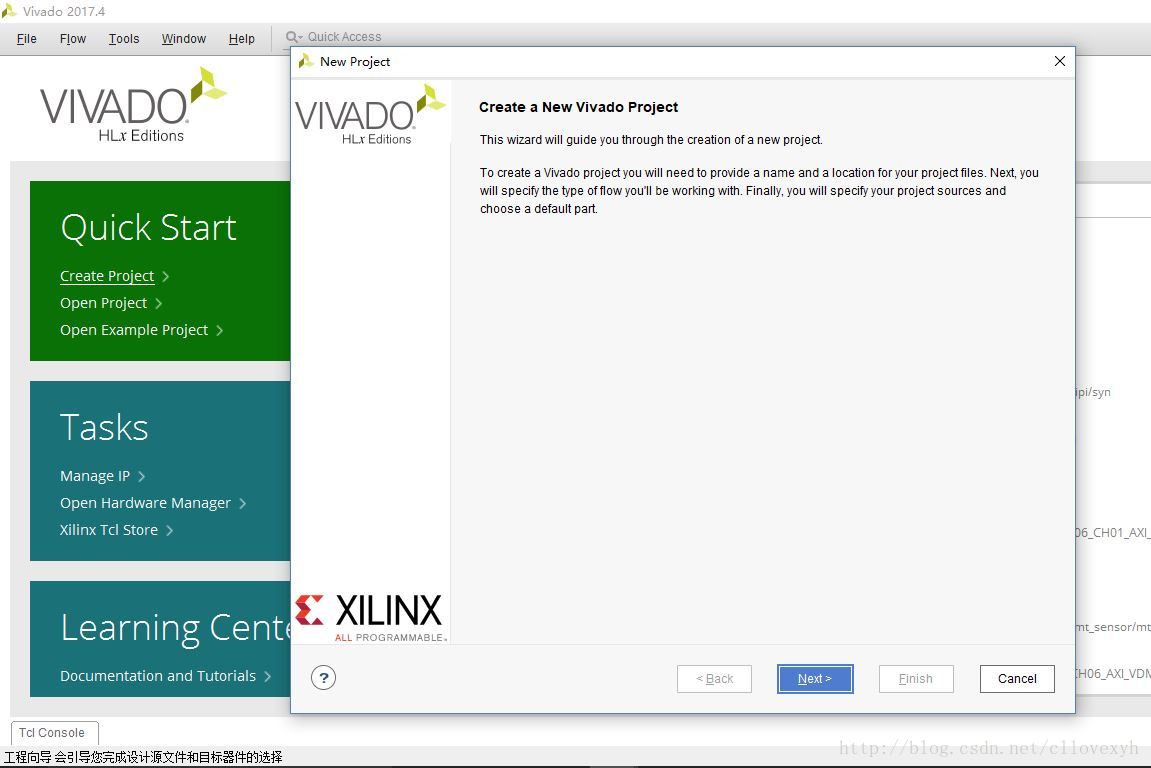

1、新建VIVADO工程,点击Next;

2、设置工程名和路径,这里设置为zedemio,点击Next;

3、选择RTL工程,点击Next;

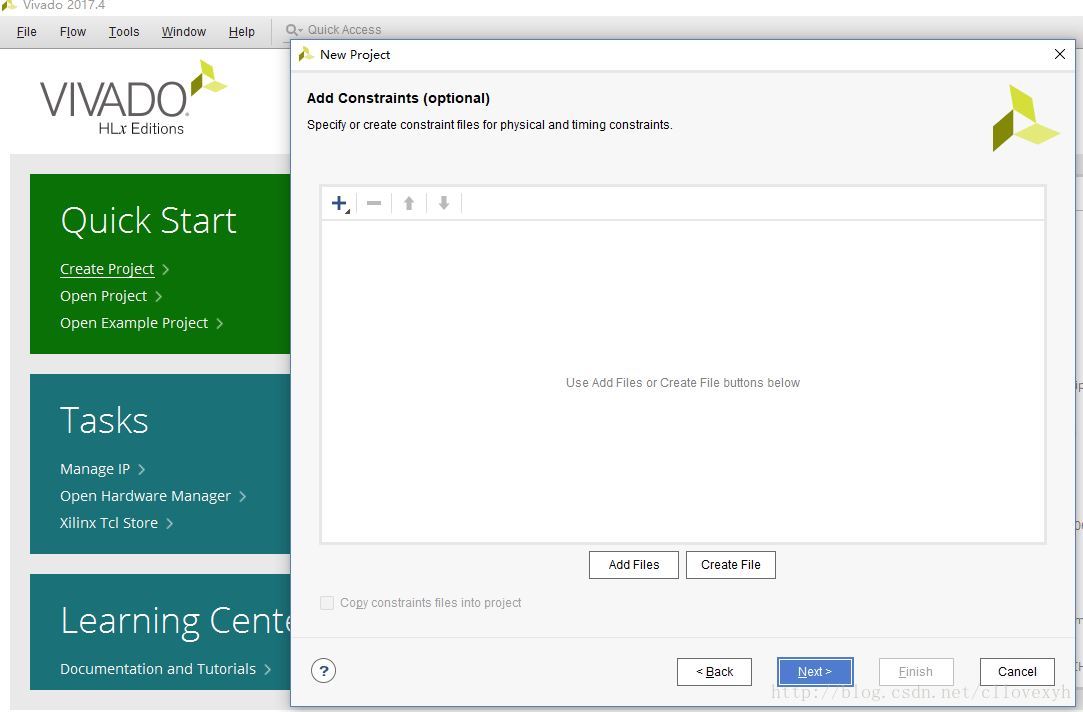

4、源文件和约束文件设置,直接Next;

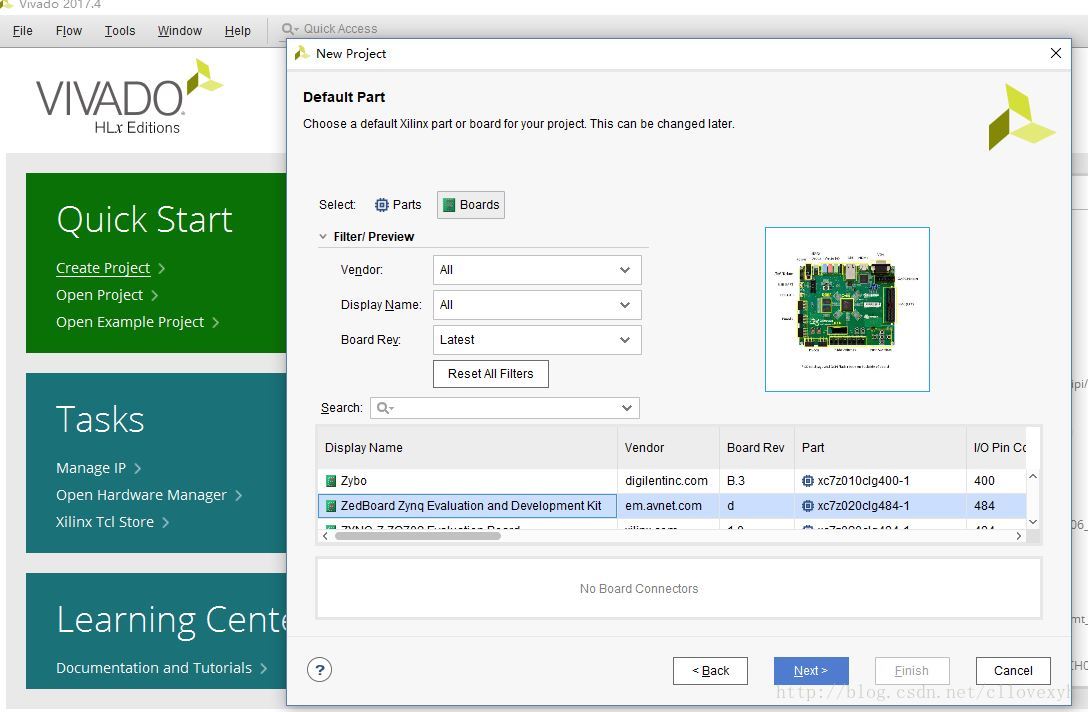

5、因为用的是ZedBoard开发板,所以在Boards中选择ZedBoard即可,点击Next,然后Finish。

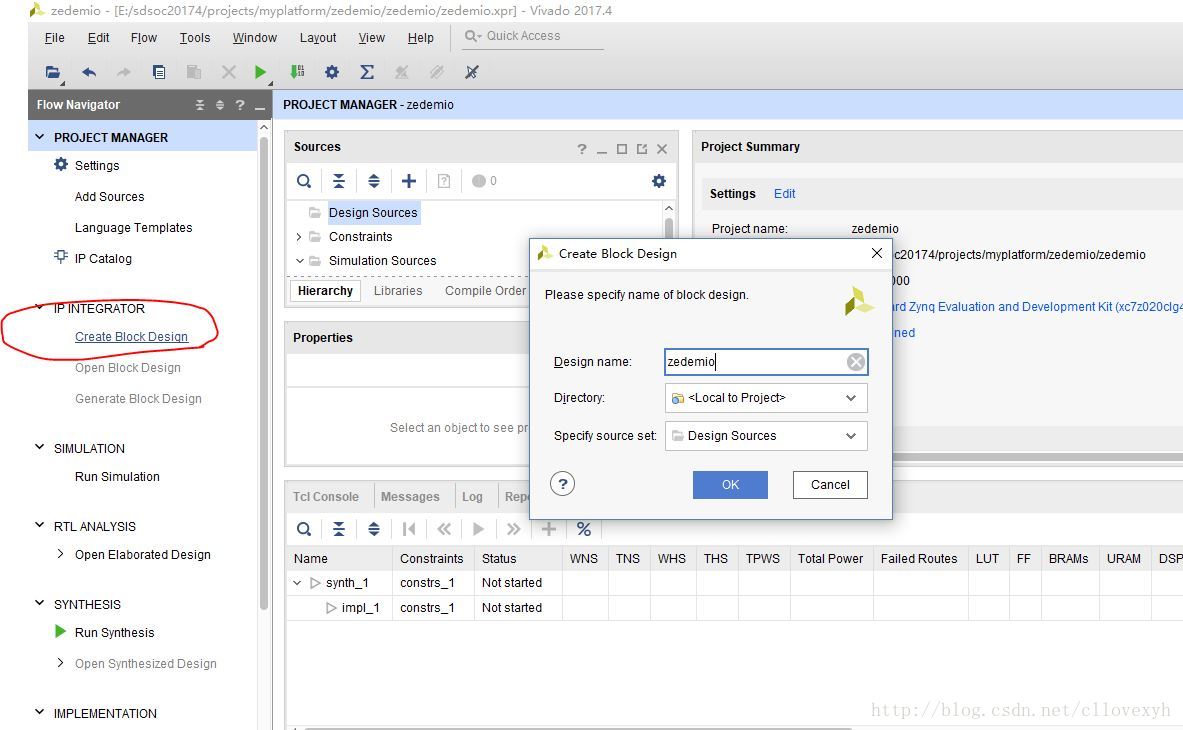

6、点击红圈所示的Create Block Design,在弹出的界面中设置Design name,注意这里设置的名字一定要和工程名一样,否则搭建的平台在运行时会报错(亲自试验过),这个要求在ug1146 中也有说明。

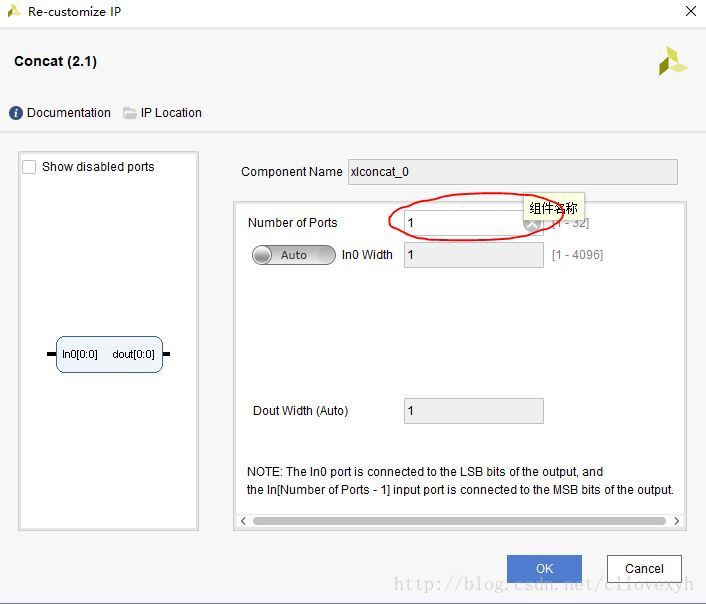

ug1146 第28页

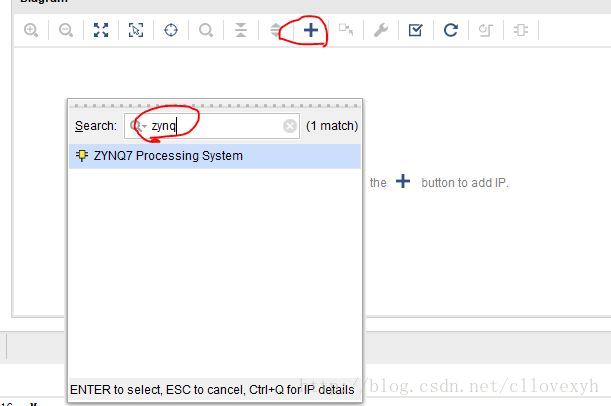

7、点击‘+’,搜索zynq,双击ZYNQ7 Processing System

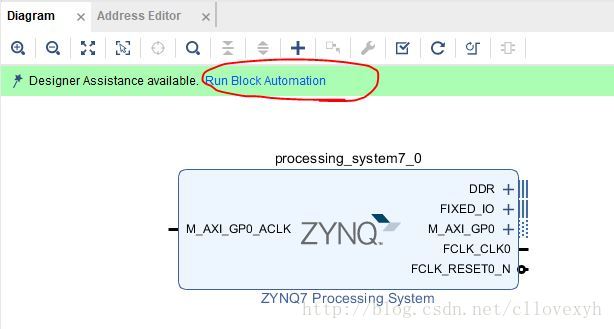

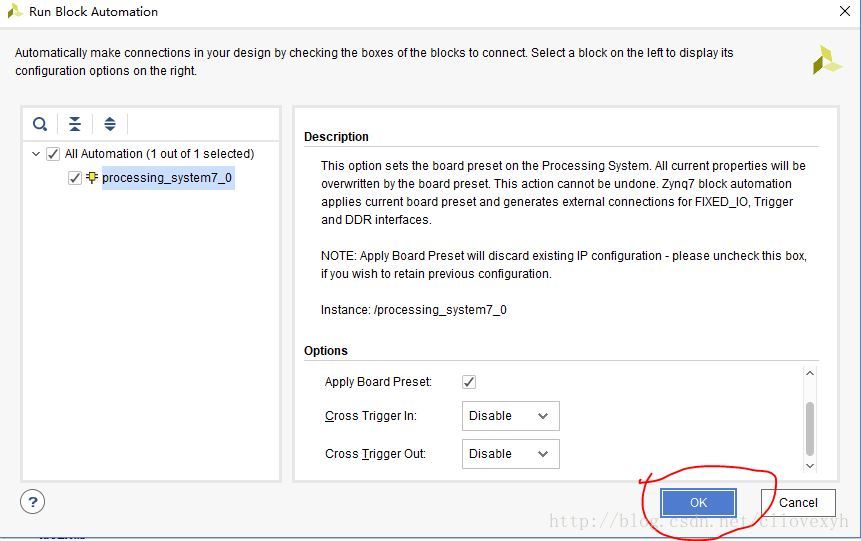

8、点击Run Block Automation->OK

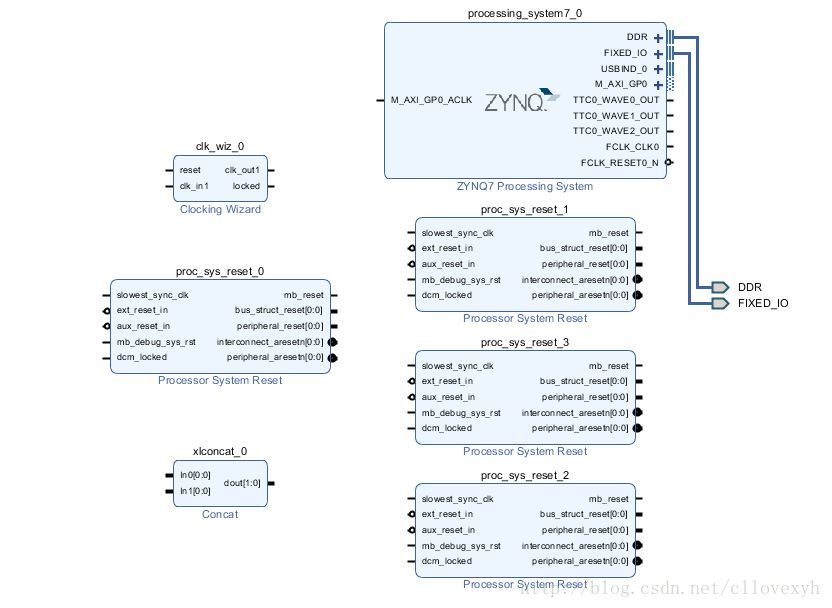

9、然后继续添加IP,如图所示

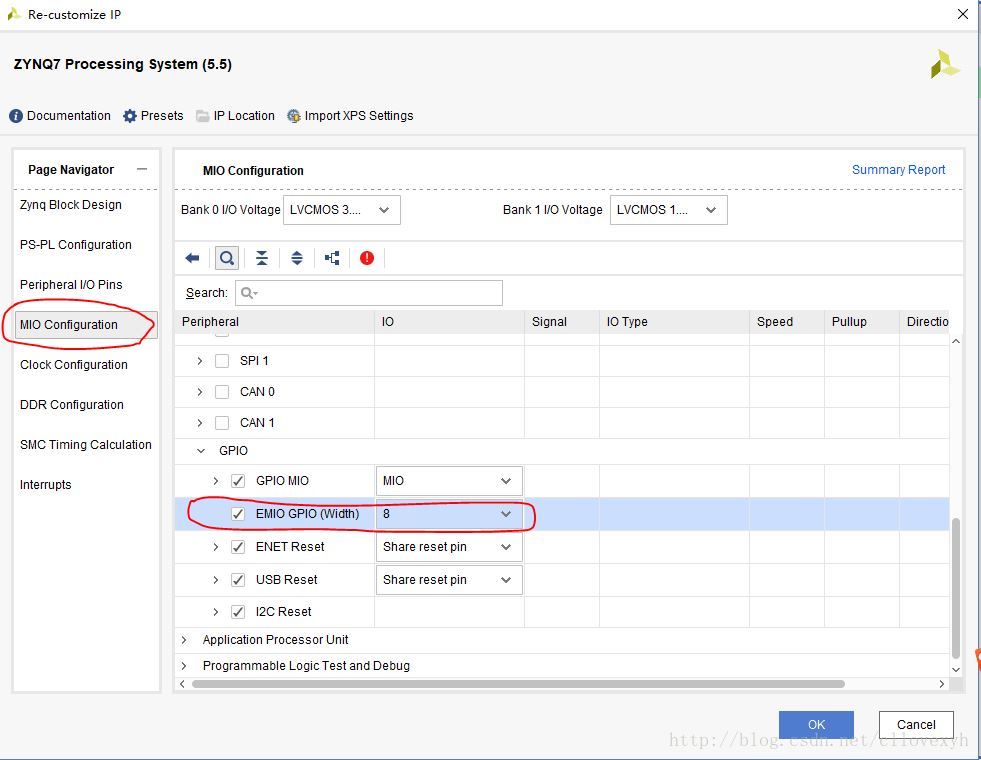

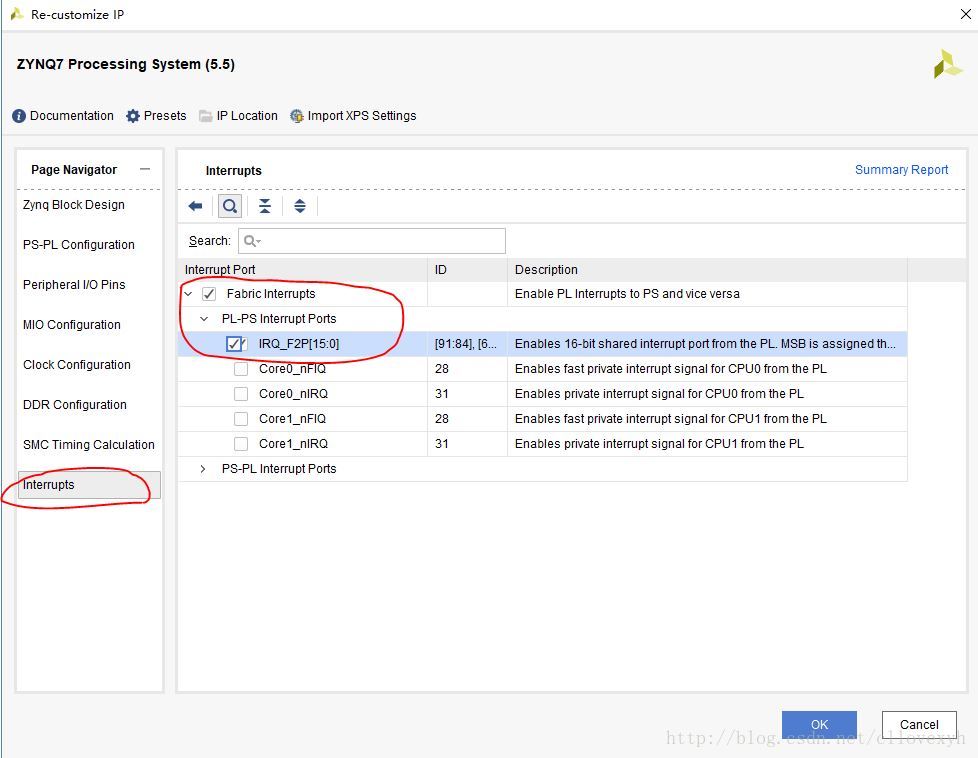

10、双击ZYNQ7 Processing System进行如下配置,然后点击OK

添加8个EMIO,因为有开发板上有8个LED。

添加PL到PS中断。

11、双击Concat进行如下配置,然后点击OK

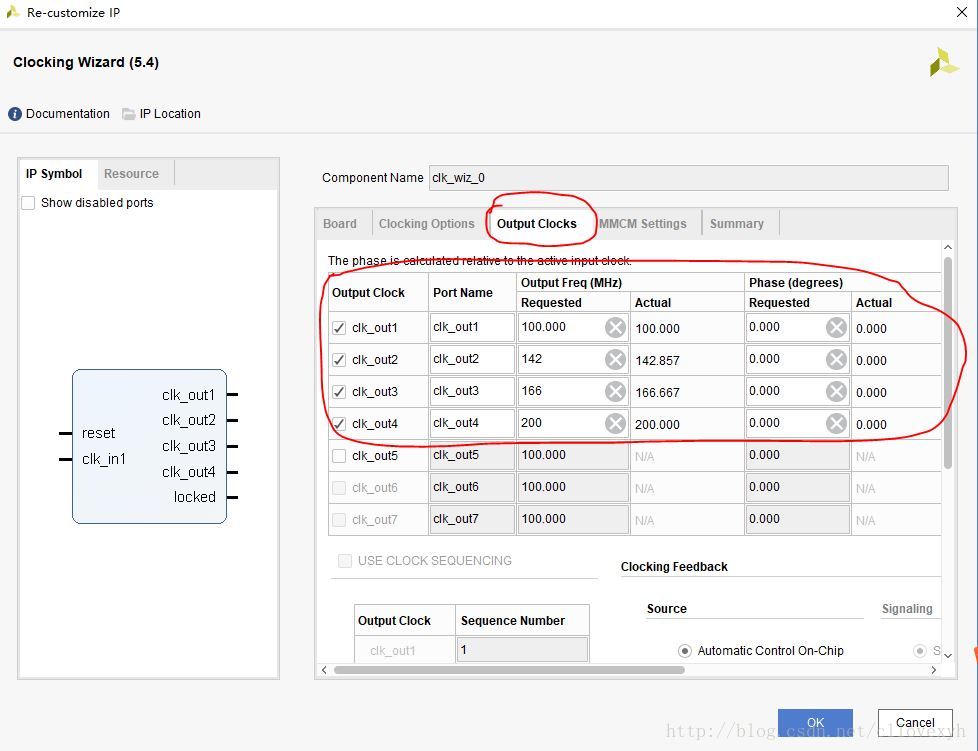

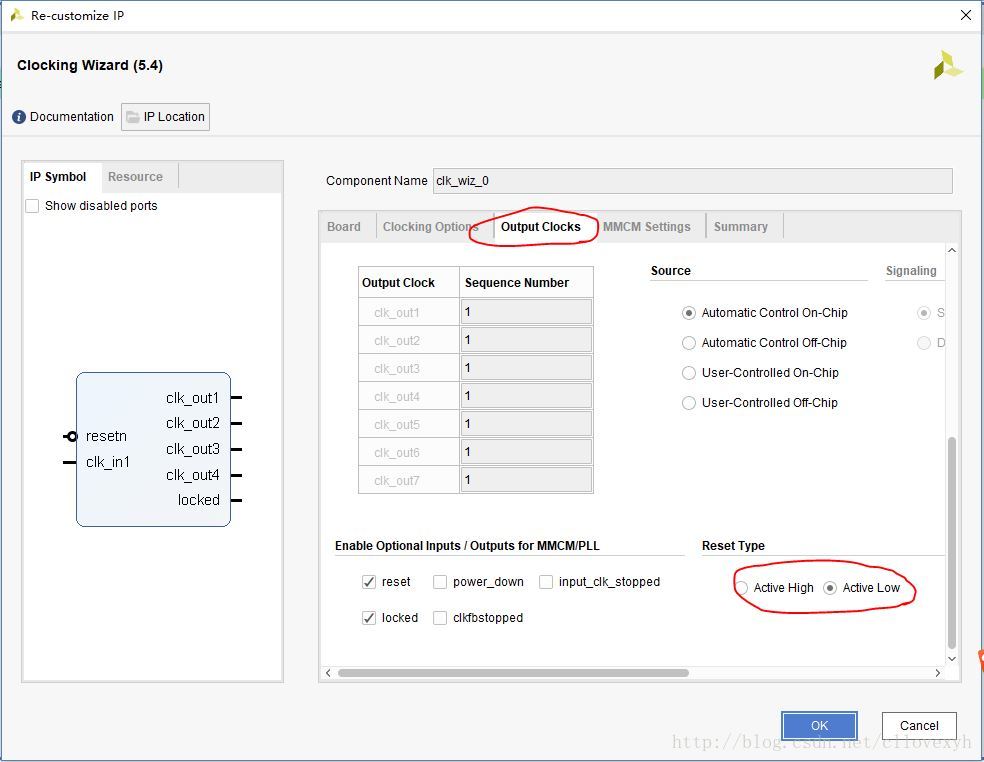

12、双击Clocking Wizard进行如下配置,然后点击OK

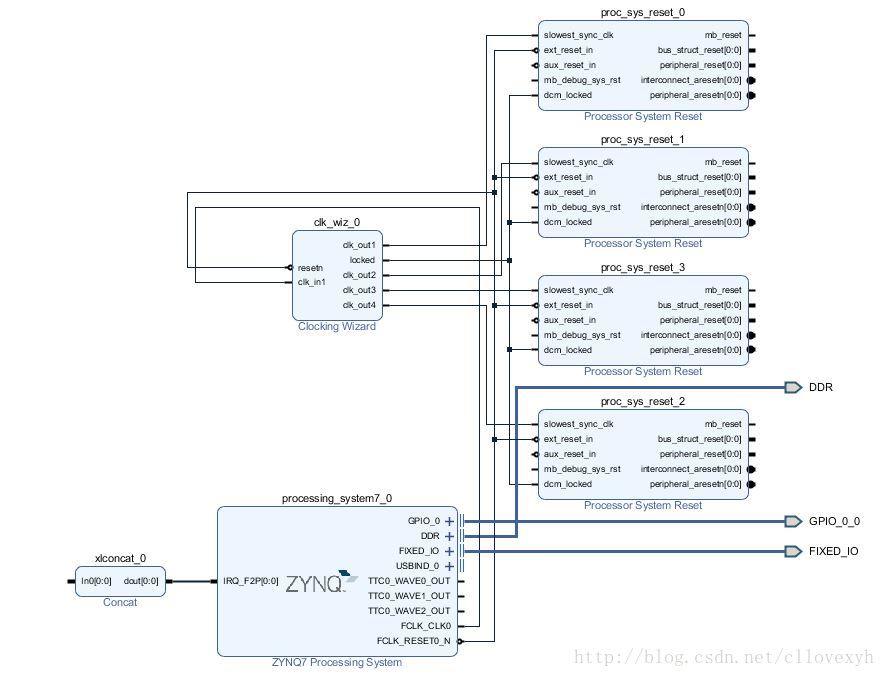

13、配置结束后就将框图连接成如下图

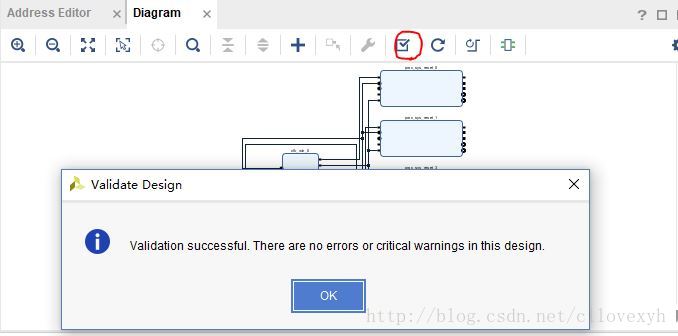

14、点击Validate Design,直到出现正确弹框,点击OK,然后Ctrl+s保存。

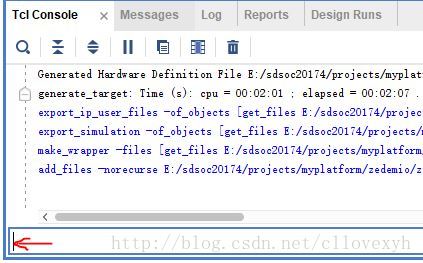

15、接下来就需要在箭头所指位置输入Tcl命令了

set_property PFM_NAME "xilinx.com:zedemio:zedemio:1.0" [get_files E:/sdsoc20174/projects/myplatform/zedemio/zedemio/zedemio.srcs/sources_1/bd/zedemio/zedemio.bd]

回车,E:/xxxxxx/zedemio.bd路径是这个工程产生bd文件的路径,在这个路径下可以找到这个工程的bd文件。

set_property PFM.CLOCK { \

clk_out1 {id "0" is_default "true" proc_sys_reset "proc_sys_reset_0" } \

clk_out2 {id "1" is_default "false" proc_sys_reset "proc_sys_reset_1" } \

clk_out3 {id "2" is_default "false" proc_sys_reset "proc_sys_reset_2" } \

clk_out4 {id "3" is_default "false" proc_sys_reset "proc_sys_reset_3" } \

} [get_bd_cells /clk_wiz_0]

set_property PFM.AXI_PORT { \

M_AXI_GP0 {memport "M_AXI_GP"} \

M_AXI_GP1 {memport "M_AXI_GP"} \

S_AXI_ACP {memport "S_AXI_ACP" sptag "ACP" memory "processing_system7_0

ACP_DDR_LOWOCM"} \

S_AXI_HP0 {memport "S_AXI_HP" sptag "HP0" memory "processing_system7_0

HP0_DDR_LOWOCM"} \

S_AXI_HP1 {memport "S_AXI_HP" sptag "HP1" memory "processing_system7_0

HP1_DDR_LOWOCM"} \

S_AXI_HP2 {memport "S_AXI_HP" sptag "HP2" memory "processing_system7_0

HP2_DDR_LOWOCM"} \

S_AXI_HP3 {memport "S_AXI_HP" sptag "HP3" memory "processing_system7_0

HP3_DDR_LOWOCM"} \

} [get_bd_cells /processing_system7_0]

set intVar []

for {set i 0} {$i < 16} {incr i} {

lappend intVar In$i {}

}

set_property PFM.IRQ $intVar [get_bd_cells /xlconcat_0]

回车,这些语句在ug1236 中都有详细的说明。

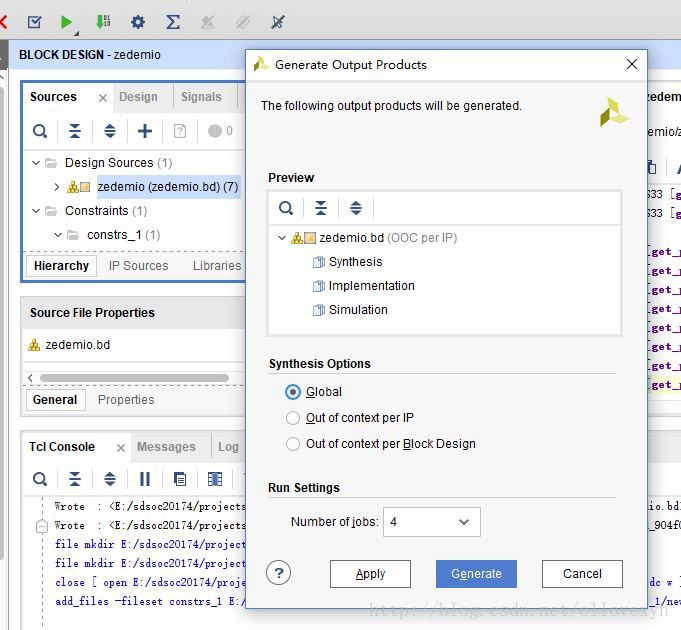

16、右击zedemio->Generate Output Products->选择Global->点击Generate

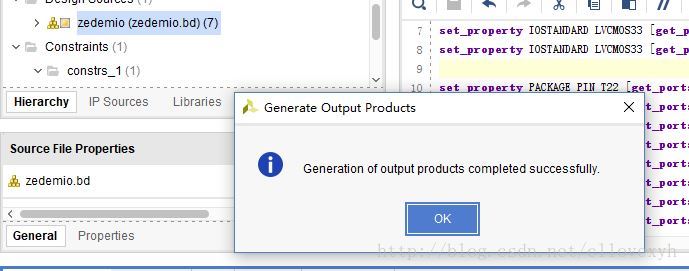

完成后点击OK

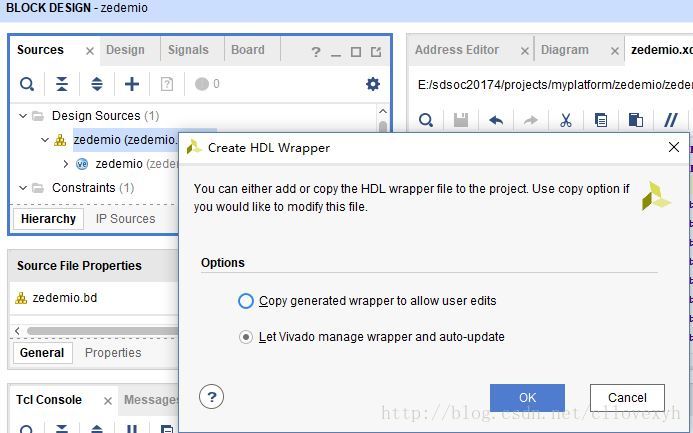

17、右击zedemio->Generate HDL Wrapper->选择auto-updata->点击OK

18、由于我们这里要点亮连接在PL上8个LED,所有需要对这些LED进行约束。

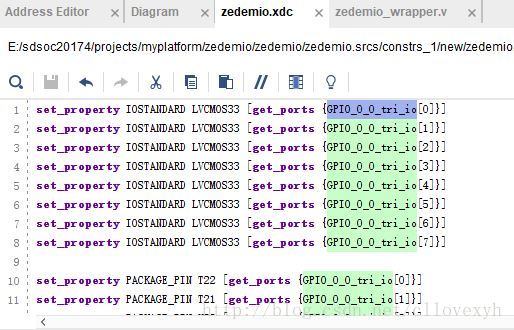

1、8个LED连接在PL上的引脚位置,如图,这8个LED分别是LD0~LD7,引脚位置分别为:T22、T21、U22、U21、V22、W22、U19、U14。

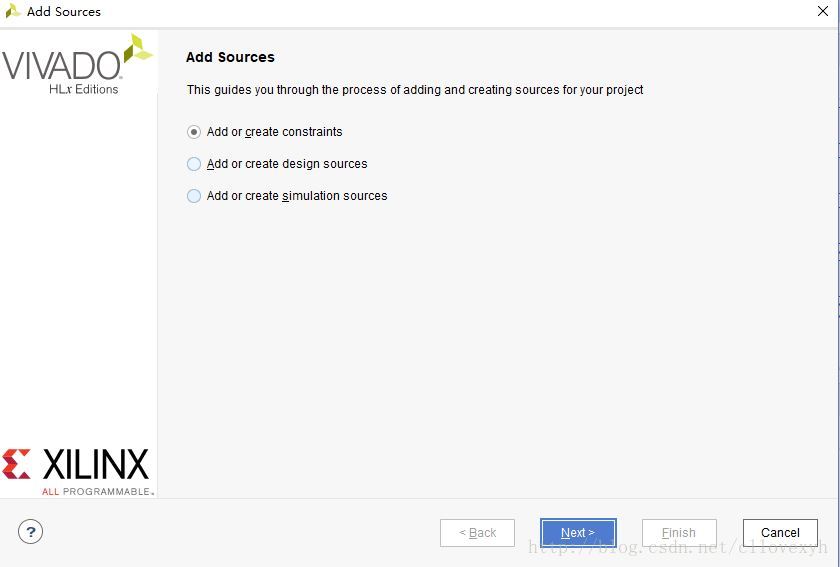

2、创建约束文件,右击Constrains->Add Sources

点击Next;

点击Create File,File name设置为zedemio,点击OK->点击Finish。

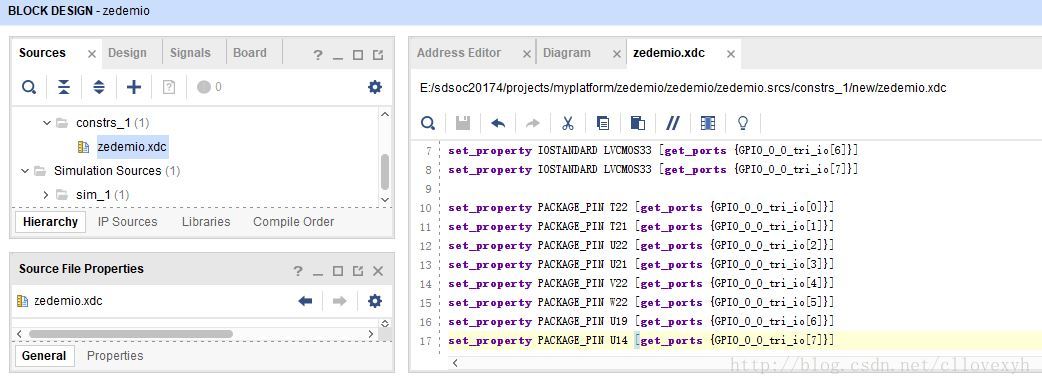

3、添加约束文件

约束文件要参照顶层文件中的接口名字进行添加

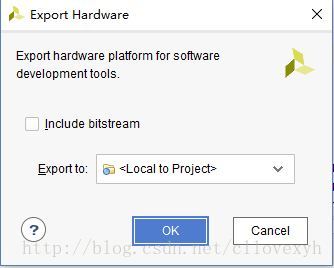

19、导出硬件,点击OK

20、输入Tcl语句,生成.dsa文件

write_dsa -force E:/sdsoc20174/projects/myplatform/zedemio/zedemio/zedemio.srcs/sources_1/bd/zedemio/zedemio.dsa

将zedemio.dsa文件生成在Tcl语句中指定的路径下

validate_dsa E:/sdsoc20174/projects/myplatform/zedemio/zedemio/zedemio.srcs/sources_1/bd/zedemio/zedemio.dsa

这样,硬件平台就搭建完成了,接着就是搭建软件平台。

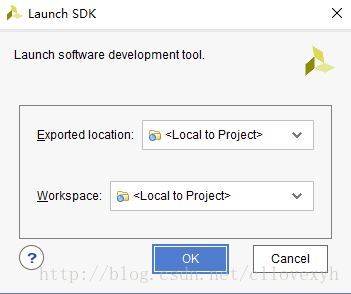

21、在当前VIVADO工程中加载SDK(方便一些),点击OK

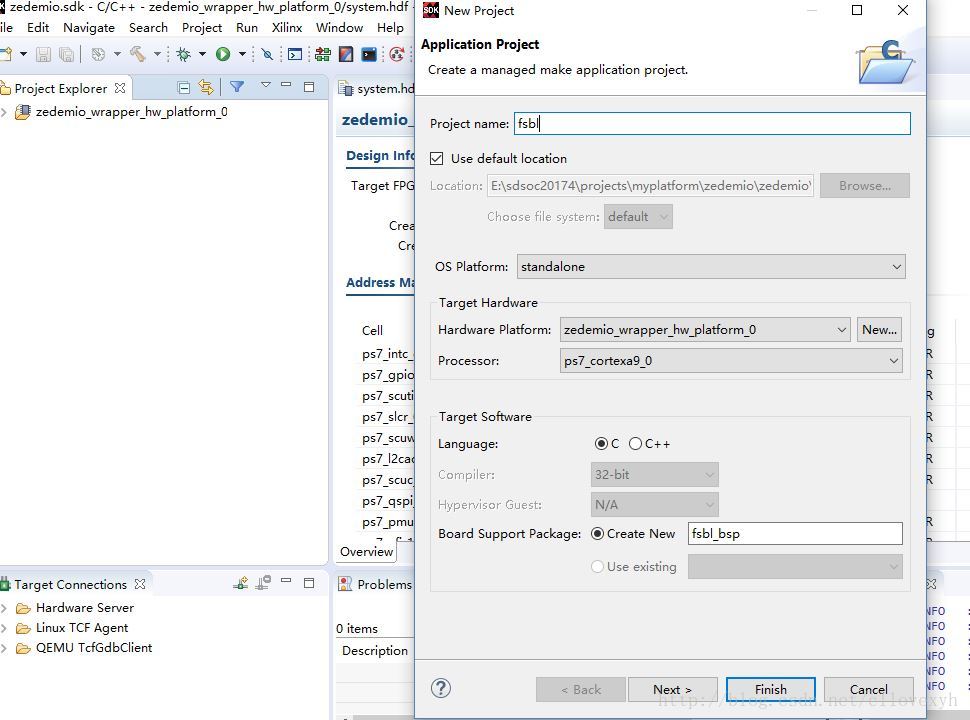

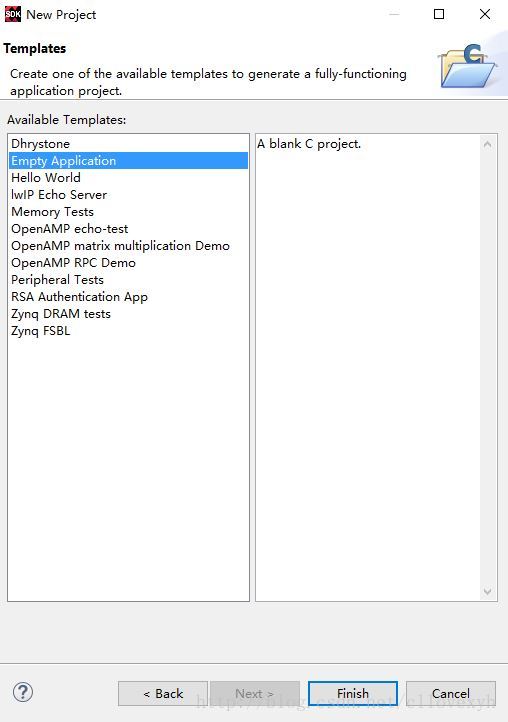

新建一个fsbl文件,点击Next;

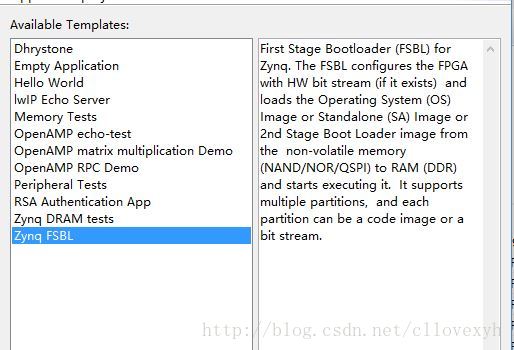

选择Zynq FSBL,然后点击Finish,等待创建完成。

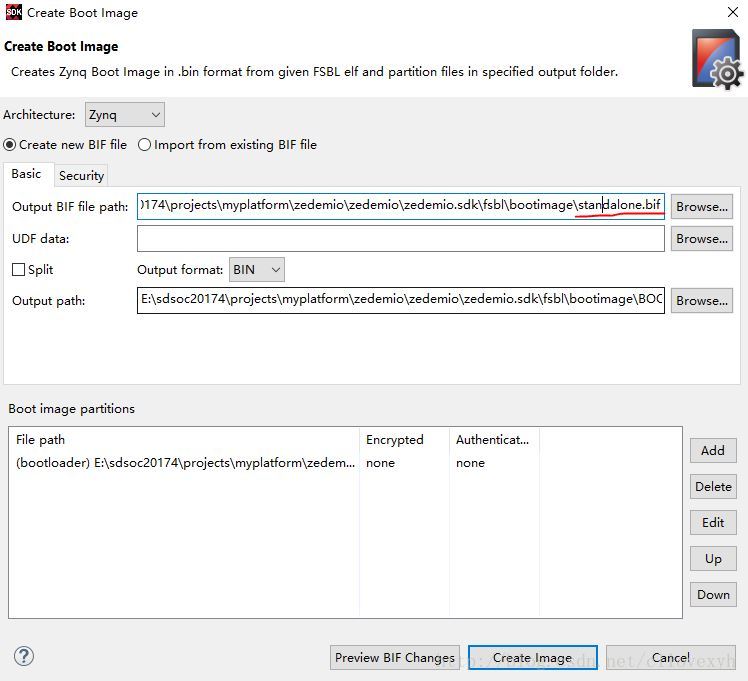

右击fsbl文件夹->Create Boot Image;修改.bif文件名,点击Create Image;

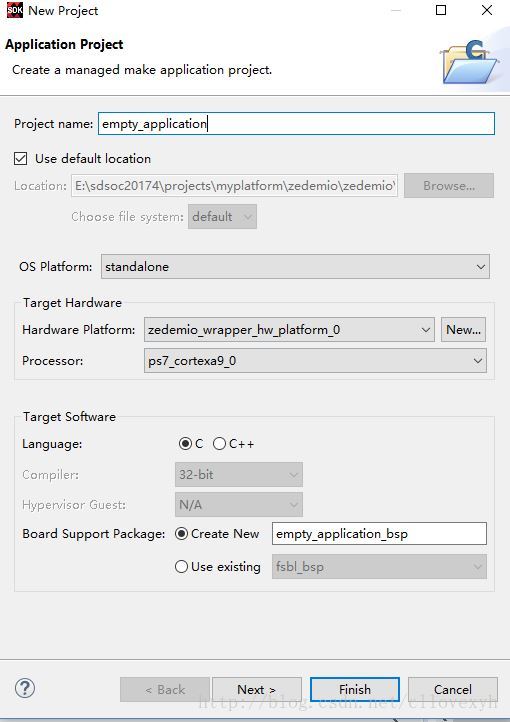

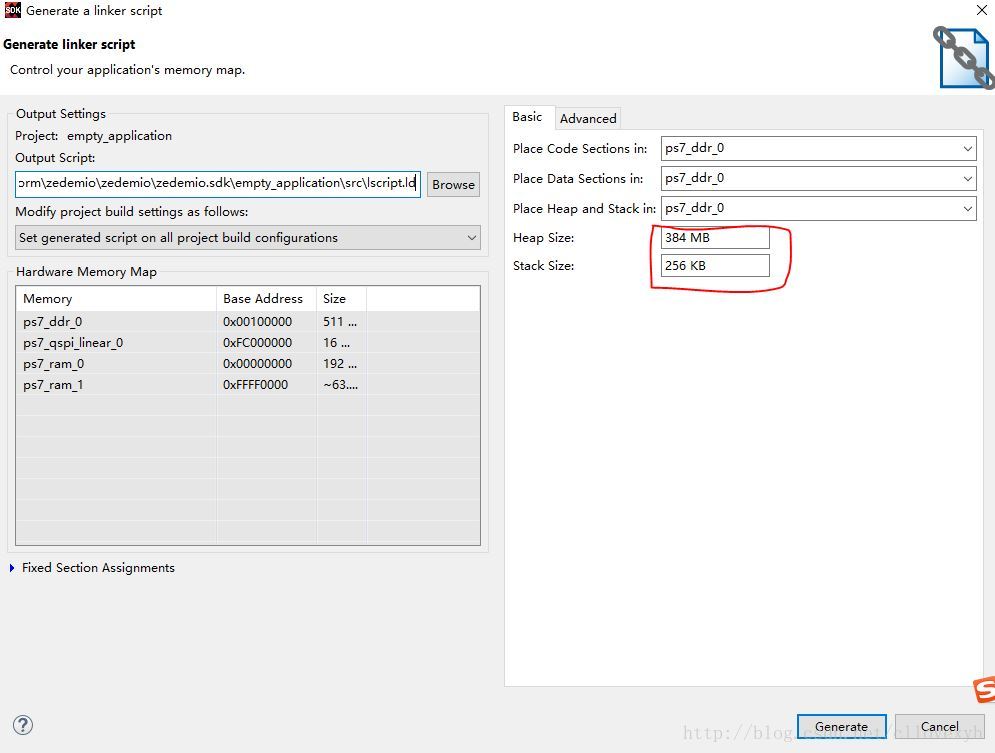

因为在SDx中,平台创建过程需要一个新的链接器脚本。这个链接器脚本基本上确保了针对自定义平台的任何应用程序代码,驻留并运行在执行板上的DDR内存中。要创建一个新的链接器脚本,我们将创建一个空应用程序。

点击Finish,等待创建完成;

完成后右击empty_application文件夹->Generate Linker Script,在Heap Size中输入402653184(384M);在Stack Size中输入262144(256K);点击Generate。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网