简介

前段时间买了一块米联客的7010开发板,打算尝试为这块开发板搭建一个简单平台。

用户自定义开发板与SDSoc直接支持的开发板的区别在于,直接支持的开发板已经根据板子上的硬件完成了一系列重要配置(如时钟、DDR型号),所以在为用户开发板搭建平台时,只需要根据该开发板的硬件实际情况进行相应的配置即可。

这里先尝试着点亮一个直接连在MIO(MIO7)上的LED。

第一步:搭建平台

平台地搭建在SDSoc学习(二)中已经进行了较为详细的描述,且大部分操作的是一样的,所以这里就着重叙述不同之处。

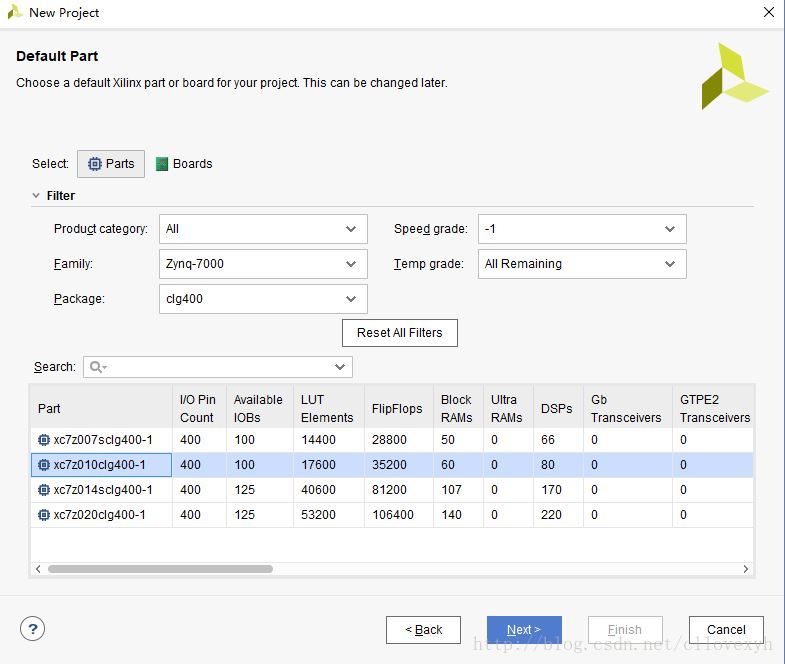

不同一:在SDSoc学习(二)中使用的是ZedBoard开发板,所以在Default Part界面中选择Boards下的ZedBoard;在这里要选择Parts,然后根据自己板子上的芯片型号进行选择,我板子上的芯片型号是xc7z010clg400-1,然后点击Next直到Finish。

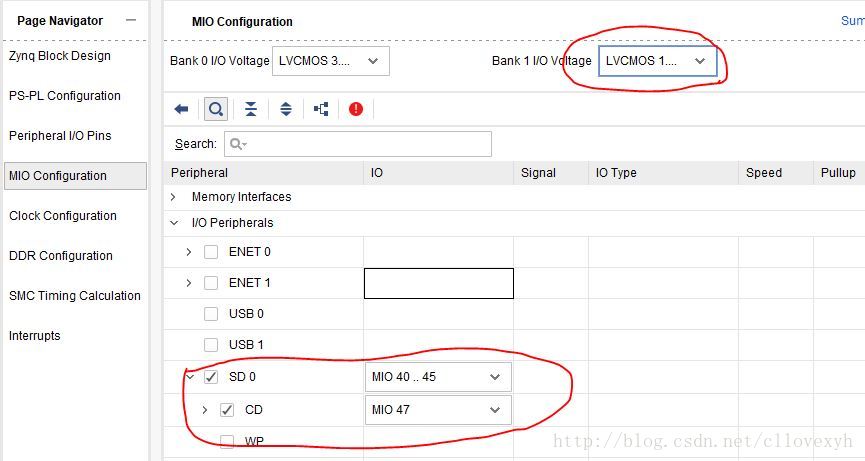

不同二:在这里我们就要配置PS部分

Bank 1 I/O Voltage设置1.8V;SD0设置管脚。

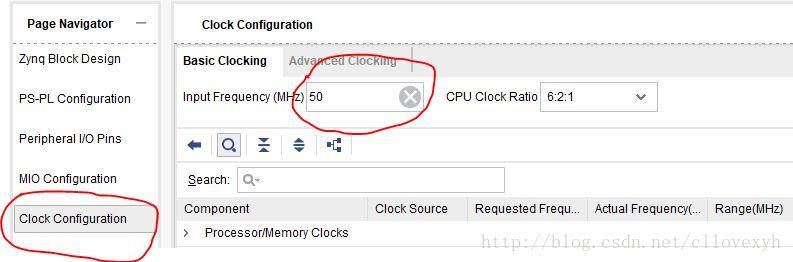

时钟设置50MHz。

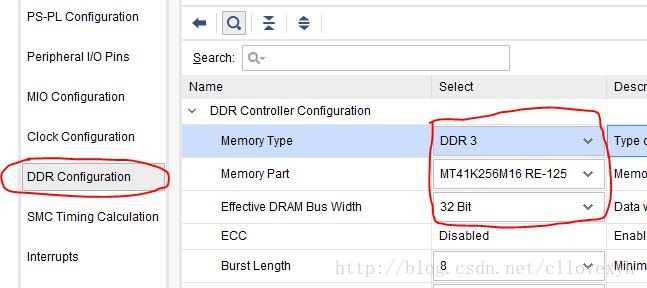

配置DDR。这些都根据用户开发板进行设置。

这里没有使用EMIO,就不需要设置EMIO,也不需要写约束文件,其他就和SDSoc学习(二)中的操作一样了。

由于这块开发板和ZedBoard一样,在MIO7上连接一个LED,所以在SDSoc中编写的程序也是一样,不需要修改,直接Debug,之后就拷贝文件到SD卡,然后通过SD卡启动就可以了。

注意

上述的几点不同之处一定要根据用户板子上的实际情况进行设置,还有,如果要SD卡启动的话,一定要在配置PS时勾选SD0或者SD1(根据实际情况而定),然后板子上要设置成SD卡启动模式(一般是拨码开关设置)。

在写Tcl命令时,有这样一条命令:set_property PFM.AXI_PORT,这条命令的作用是声明PS上的接口,而这些被声明接口被用在SDSoc做硬件加速时,实现PS与PL之间数据传输。

完整的声明接口命令如下:

set_property PFM.AXI_PORT { \

M_AXI_GP0 {memport "M_AXI_GP"} \

M_AXI_GP1 {memport "M_AXI_GP"} \

S_AXI_ACP {memport "S_AXI_ACP" sptag "ACP" memory "ps7 ACP_DDR_LOWOCM"} \

S_AXI_HP0 {memport "S_AXI_HP" sptag "HP0" memory "ps7 HP0_DDR_LOWOCM"} \

S_AXI_HP1 {memport "S_AXI_HP" sptag "HP1" memory "ps7 HP1_DDR_LOWOCM"} \

S_AXI_HP2 {memport "S_AXI_HP" sptag "HP2" memory "ps7 HP2_DDR_LOWOCM"} \

S_AXI_HP3 {memport "S_AXI_HP" sptag "HP3" memory "ps7 HP3_DDR_LOWOCM"} \

} [get_bd_cells /ps7]

以下是我搭建一个使用了M_AXI_GP0接口来连接一个AXI_GPIO的IP的平台,Tcl命令声明接口如下:

set_property PFM.AXI_PORT { \

M_AXI_GP1 {memport "M_AXI_GP"} \

S_AXI_ACP {memport "S_AXI_ACP" sptag "ACP" memory "ps7 ACP_DDR_LOWOCM"} \

S_AXI_HP1 {memport "S_AXI_HP" sptag "HP1" memory "ps7 HP1_DDR_LOWOCM"} \

S_AXI_HP2 {memport "S_AXI_HP" sptag "HP2" memory "ps7 HP2_DDR_LOWOCM"} \

S_AXI_HP3 {memport "S_AXI_HP" sptag "HP3" memory "ps7 HP3_DDR_LOWOCM"} \

} [get_bd_cells /processing_system7_0]

不同在于第二个声明接口的语句块中,没有声明M_AXI_GP0,这是用于声明了的接口将有可能在SDSoc中做硬件加速时被用于数据传输,而我搭建的平台不希望SDSoc使用M_AXI_GP0,因此就不声明M_AXI_GP0,同理,在以后搭建平台时,如果不希望SDSoc使用某些接口,那么就不声明这些接口即可,详细解释请查阅官方资料ug1146。

结束

通过搭建这个平台,我发现其实只要在VIVADO下能运行的工程,都可以被设置成为硬件平台,但需要注意根据实际硬件进行配置,以及注意写Tcl命令声明接口。

本文转载自:CLGo的博客

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网