从Vivado开始,配置GTX的时候,多了一个SATA协议支持,但有些小地方还需要自己另外设置。整理了一下,分享给大家。

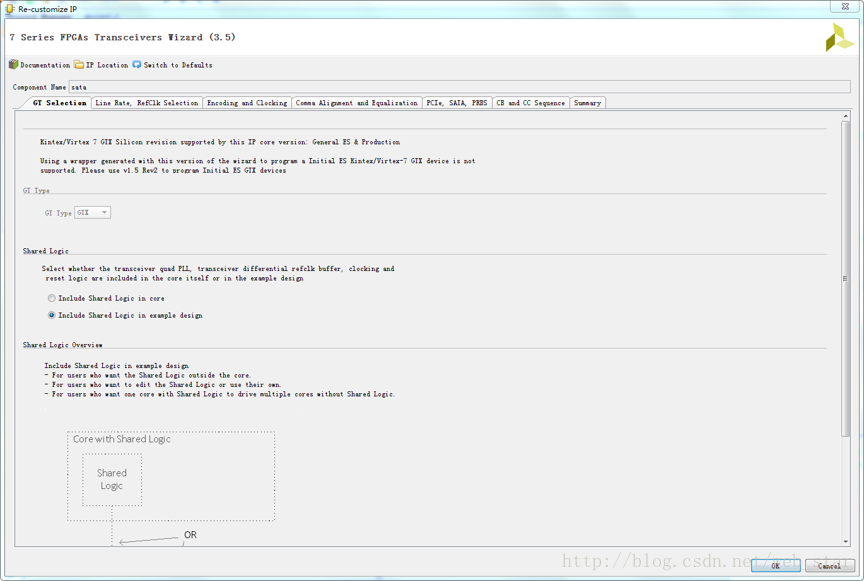

首先打开Transceivers wizard:

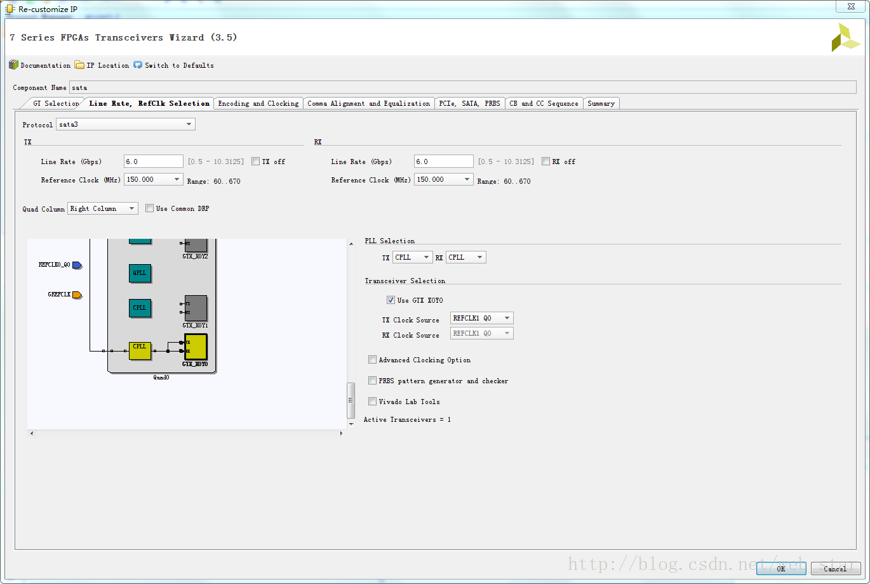

打开页签,线速率和参考时钟选择,在协议里面选择SATA2或者SATA3,设置参考时钟。

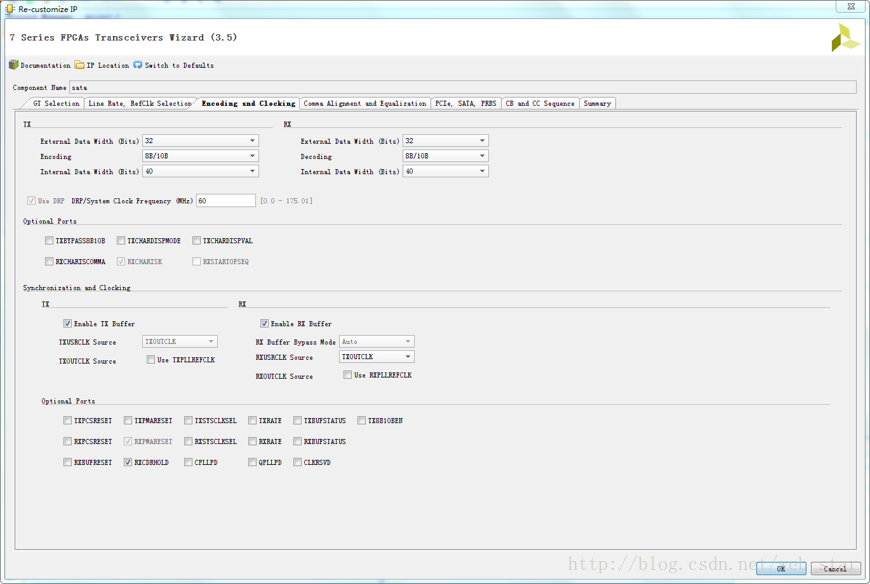

选择编码和时钟设置,设置外部数据宽度为32位,内部40bit,8B/10B编码,使能收发缓存,全部使用发送时钟。

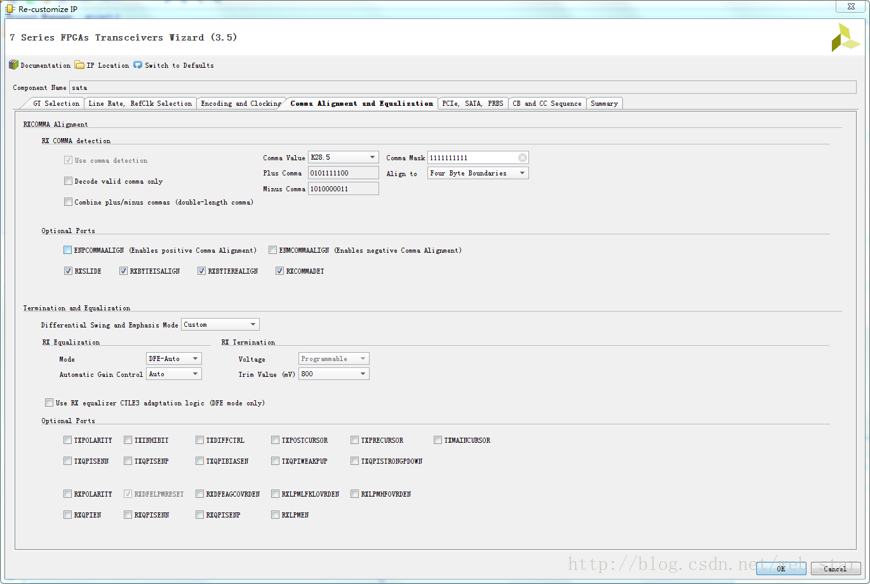

打开设置K码对齐和均衡,设置K码为28.5,mask全部设置为1,因为之前设置的是32bit,这里选择对齐到4字节。接收均衡看工作频率和传输线缆长度,短距离和频率低情况下,选择LPM,高频率和长线缆设置DFE。

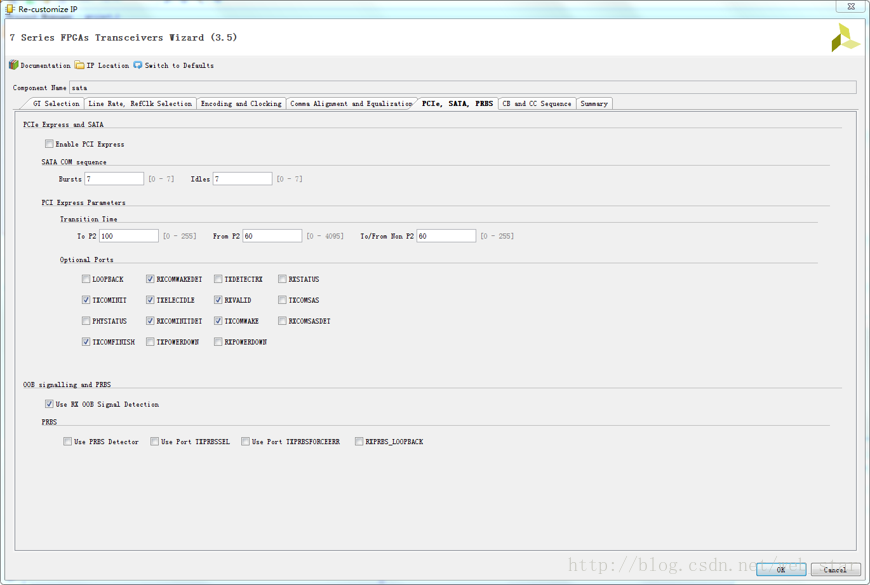

打开PCIE,SATA,PRBS页,这里需要把OOB检测勾选上,其它的信号如果有使用,也需要勾选上。

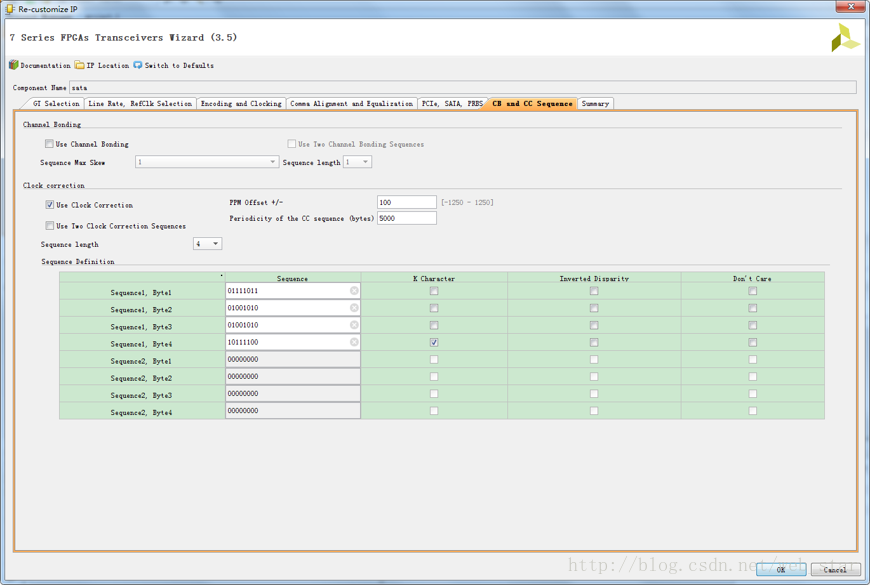

打开时钟校正和绑定选项页,这里需要配置时钟校正,由于SATA协议里面有ALIGN字符,所以需要设置为对应ALIGN字符的编码,7B4A4ABCh,其中BC是K28.5码字。

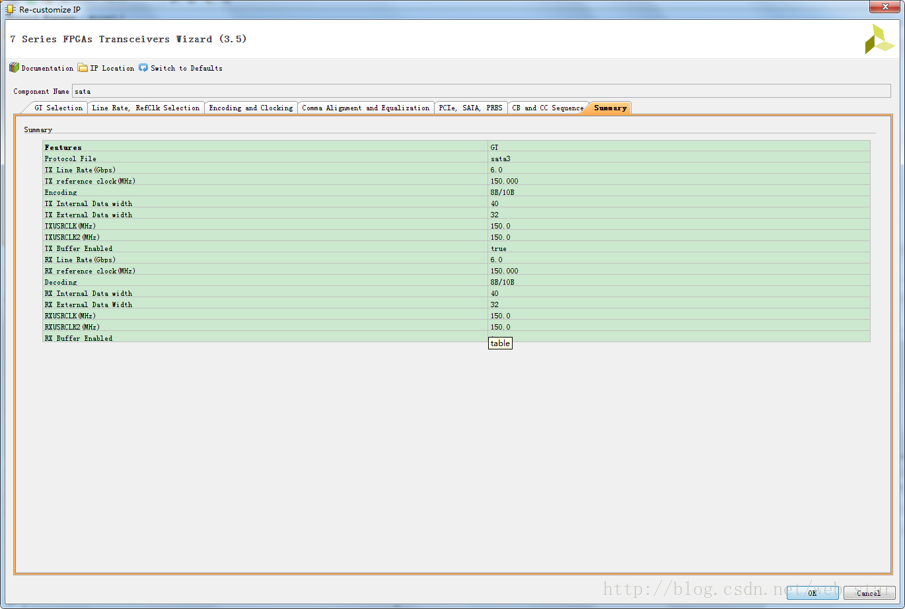

打开总览页,到此就全部设置完成了。

本文转载自: https://blog.csdn.net/web_star/article/details/78584443

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网