对于FPGAs这样的可编程解决方案,传统的想法是您必须愿意为它们的灵活性做出大量的权衡。在许多情况下确实是这样。即使只是通过芯片获取数据也会消耗掉宝贵的路由资源,增加大量的开销。当需要大规模或快速转移时,这些问题就会加剧。在基于ASIC的SoCs中,很容易为高速接口添加IP。然而,在fpga中,有价值的逻辑单元常常被用来实现这些相同的接口。事实证明,使用asic中用于连接模块的一种解决方案也是fpga的一大优势。晶片上网络(Noc)在ASIC中使用了很多,现在他们在FPGA中找到了归宿。FPGA使用Noc带来的好处可能会让你大吃一惊。

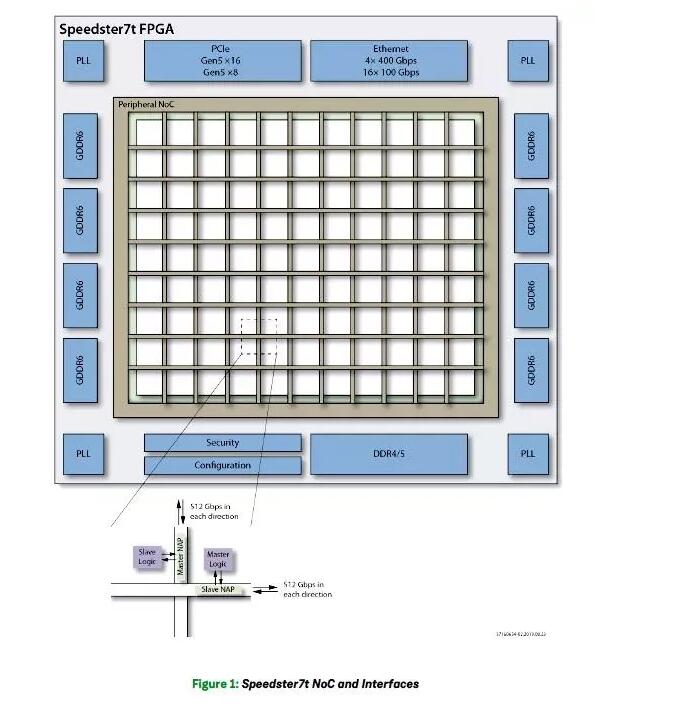

Achronix撰写了一份有趣的白皮书,其中涵盖了在Speedster7t FPGA中增加NoC带来的八项好处。他们的NoC专为满足FPGA的需求而设计。它排列在垂直和水平通道中,这些通道穿过FPGA内核。每个通道具有两个以512 Gbps速度运行的单向高速总线。FPGA还保留了其传统的FPGA路由结构。位于行和列相交处的NoC接入点(NAP)用于建立与NoC的连接。NoC连接到所有用于内存和网络的外部接口。

在这里,我们不会具体介绍这八项好处中的每一项(文末可以下载白皮书),仅讨论其中的一部分。

连接到PCIe和400G以太网的能力有两个好处。在FPGA中进行PCIe接口设计时需要繁琐的工作,以了解布局和路由,从而管理延迟和吞吐量。使用NoC,许多以前需要时间和FPGA资源的工作将自动处理。不仅节省了设计时间,而且减少了测试和调试。

NoC也推动了400G以太网的发展。使用其新的数据包模式,传入的数据包可在四个独立的256位总线上并行级联,从而有效地传输数据包。数据包通过这四个总线交错,因此FPGA可以有效地跟上输入数据流的速度。

其中一个令人惊讶的好处与多个团队如何在包含NoC的FPGA项目上更有效地工作有关。传统上,由于在FPGA结构中访问互连资源时存在冲突,团队设计难以执行。使用Achronix Speedster7t NoC, FPGA中的任何设计块都可以通过连接到NoC的NAP访问任何其他设计块。这将从设计考虑中删除关于放置或互连资源的任何问题。

此外NoC及其高性能FPGA架构是一个成功的组合。由于在Speedster7t中采用了专门设计的机器学习处理器(MLP),因此对于机器学习应用尤其如此。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网