本文来自EETOP Blog,原文地址:http://www.eetop.cn/blog/html/14/56214-20411.html

本文翻译自Using Digital Clock Managers (DCMs) in Spartan-3 FPGAs

DCM主要功能

1. 分频倍频:DCM可以将输入时钟进行multiply或者divide,从而得到新的输出时钟。

2. 去skew:DCM还可以消除clock的skew,所谓skew就是由于传输引起的同一时钟到达不同地点的延迟差。

3. 相移:DCM还可以实现对输入时钟的相移输出,这个相移一般是时钟周期的一个分数。

4. 全局时钟:DCM和FPGA内部的全局时钟分配网络紧密结合,因此性能优异。

5. 电平转换:通过DCM,可以输出不同电平标准的时钟。

DCM的特点与能力(Spartan-3系列为例)

- 数量:4 DCM / FPGA(也有例外)

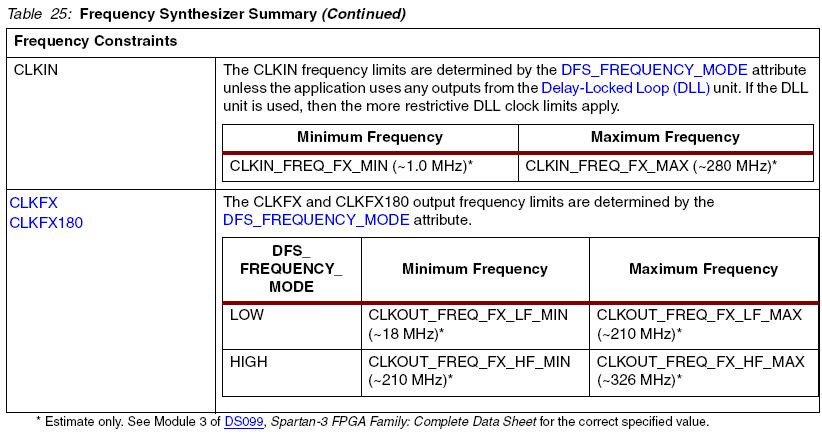

-- 应该够用了 - 数字频率综合器输入(CLKIN):1-280MHz

- 延迟锁相环输入(CLKIN):18-280MHz

- 时钟输入源(CLKIN):

Global buffer input pad

Global buffer output

General-purpose I/O (no deskew)

Internal logic (no deskew)

-- 上面最后两个分别是外部的普通IO口和内部的逻辑,没有deskew,所以时钟质量不会很好。 - 频率综合器输出(CLKFX、CLKFX180):是CLKIN的M/D倍,其中

M=2..32

D=1..32

-- 这样看来最大能倍频32倍,最小能16分频。 - 时钟dividor输出(CLKDV):是CLKIN的下列分频

1.5, 2, 2.5, 3, 3.5, 4, 4.5, 5, 5.5, 6, 6.5, 7, 7.5, 8, 9, 10, 11, 12, 13, 14, 15, or 16

-- 发现没有,最大的分频也是16。不过能支持半分频,比用频率综合器方便。 - 倍频输出(CLK2X、CLK2X180):CLKIN的2倍频

- 时钟conditioning、占空比调整:这个对所有时钟输出都施加,占空比为50%。

- 1/4周期相移输出(CLK0/90/180/270):是CLKIN的1/4周期相移输出。

- 半周期相移输出(CLK0/180、CLK2X/180、CLKFX/180):相差为180度的成对时钟输出。

- 相移精度:最高精度为时钟周期的1/256。

- 时钟输出:9个

到全局时钟网的时钟输出:最多9个中的4个

到General purpose互联:最多9个

到输出脚:最多9个

-- 可见9个时钟输出可以随意链接内部信号或者外部输出,但是进入全局时钟网的路径最多只有4个。

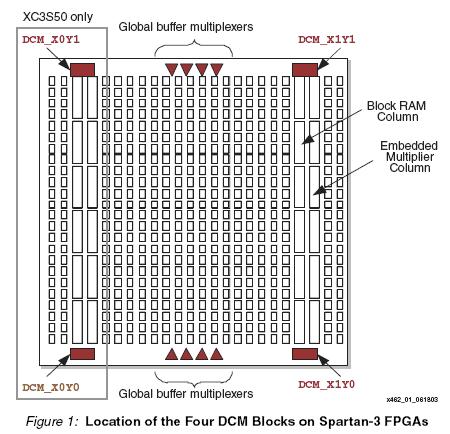

DCM的位置在哪?

我们以Spartan3系列为例。

FPGA看上去就是一个四方形。最边缘是IO pad了。

除去IO pad,内部还是一个四方形。

四个角上各趴着一个DCM。

上边缘和下边缘中间则各趴着一个全局Buffer的MUX。

这样的好处是四个DCM的输出可以直接连接到全局Buffer的入口。

下面是手绘简图,很丑是吧,呵呵。

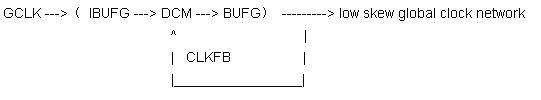

DCM是全局时钟网络可选的一部分

一般,时钟通过一个“全局输入buffer”和“全局时钟buffer” 进入全局时钟网络。如下所示

GCLK --->( IBUFG ---> BUFG) ---> low skew global clock network

在需要的时候,DCM也成为全局时钟网络的一环。

DCM 内部构成一览

1. DLL 延迟锁定环

说是延迟锁定环,但是我觉得叫做延迟补偿环更加贴切。因为DLL的主要功能是消除输入时钟和输出时钟之间的延迟,使得输入输出在外部看来是透明连接。

实现这种功能的原理是:DLL通过输出时钟CLK0或者CLK2X观察实际的线路延迟,然后在内部进行补偿。

一句话,DLL的核心功能是无延迟。

DLL的输出是CLK0, CLK90, CLK180, CLK270, CLK2X, CLK2X180, 和 CLKDV。

2. DFS 数字频率综合

DFS的主要功能是利用CLKIN合成新的频率。

合成的参数是:M(multiplier)和 D(divisor)。通过MD的组合实现各种倍频和分频。

如果不使用DLL,则DFS的合成频率和CLKIN就不具有相位关系,因为没有延迟补偿,相位就不再同步。

3. PS 相位偏移

注意这个相位偏移不是DLL中输出CLK90/180/270用的。这个PS可以令DCM的所有9个输出信号都进行相位的偏移。偏移的单位是CLKIN的一个分数。

也可以在运行中进行动态偏移调整,调整的单位是时钟的1/256。

这个功能我们平时不常用。

4. 状态逻辑

这个部分由 LOCKED 信号和 STATUS[2:0] 构成。LOCKED信号指示输出是否和CLKIN同步(同相)。STATUS则指示DLL和PS的状态。

DCM_BASE

DCM_BASE是基本数字时钟管理模块的缩写,是相位和频率可配置的数字锁相环电路,常用于FPGA系统中复杂的时钟管理。如果需要频率和相位动态重配置,则可以选用DCM_ADV原语;如果需要相位动态偏移,可使用DCM_PS原语。DCM系列原语的RTL结构如图3-8所示。

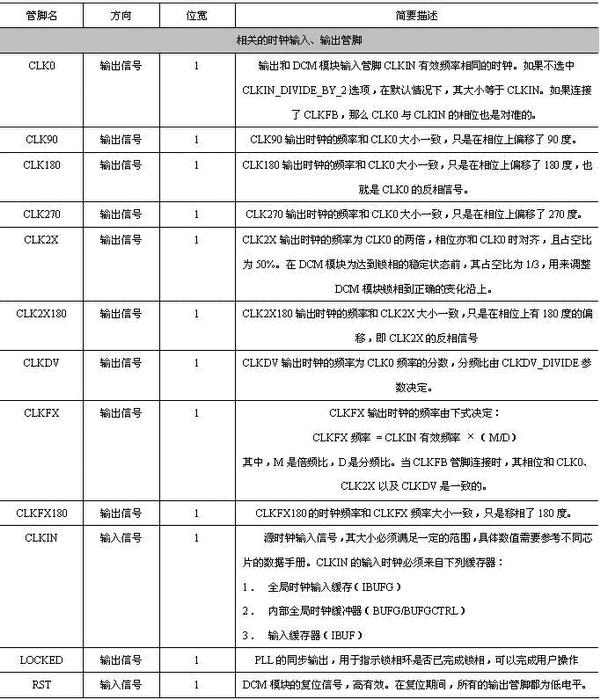

模块接口信号的说明如表3-8所列。

DCM_BASE组件可以通过Xilinx的IP Wizard向导产生,也可以直接通过下面的例化代码直接使用。其Verilog的例化代码模板为:

// DCM_BASE: 基本数字时钟管理电路(Base Digital Clock Manager Circuit)

// 适用芯片:Virtex-4/5

// Xilinx HDL库向导版本,ISE 9.1

DCM_BASE #(

.CLKDV_DIVIDE(2.0),

// CLKDV分频比可以设置为: 1.5,2.0,2.5,3.0,3.5,4.0,4.5,5.0,5.5,6.0,6.5

// 7.0,7.5,8.0,9.0,10.0,11.0,12.0,13.0,14.0,15.0 or 16.0

.CLKFX_DIVIDE(1), // Can be any integer from 1 to 32

// CLKFX信号的分频比,可为1到32之间的任意整数

.CLKFX_MULTIPLY(4),

// CLKFX信号的倍频比,可为2到32之间的任意整数

.CLKIN_DIVIDE_BY_2("FALSE"),

// 输入信号2分频的使能信号,可设置为TRUE/FALSE

.CLKIN_PERIOD(10.0),

// 指定输入时钟的周期,单位为ns,数值范围为1.25~1000.00。

.CLKOUT_PHASE_SHIFT("NONE"),

// 指定移相模式,可设置为NONE或FIXED

.CLK_FEEDBACK("1X"),

// 指定反馈时钟的频率,可设置为NONE、1X或2X。相应的频率关系都是针对CLK0而言的。

.DCM_PERFORMANCE_MODE("MAX_SPEED"),

// DCM模块性能模式,可设置为 MAX_SPEED 或 MAX_RANGE

.DESKEW_ADJUST("SYSTEM_SYNCHRONOUS"),

// 抖动调整,可设置为源同步、系统同步或0~15之间的任意整数

.DFS_FREQUENCY_MODE("LOW"),

// 数字频率合成模式,可设置为LOW或HIGH 两种频率模式

.DLL_FREQUENCY_MODE("LOW"),

// DLL的频率模式,可设置为LOW、HIGH或HIGH_SER

.DUTY_CYCLE_CORRECTION("TRUE"),

// 设置是否采用双周期校正,可设为TRUE或FALSE

.FACTORY_JF(16'hf0f0),

// 16比特的JF因子参数

.PHASE_SHIFT(0),

// 固定相移的数值,可设置为 -255 ~ 1023之间的任意整数

.STARTUP_WAIT("FALSE")

// 等DCM锁相后再延迟配置DONE管脚,可设置为TRUE/FALSE

) DCM_BASE_inst (

.CLK0(CLK0), // 0度移相的DCM时钟输出

.CLK180(CLK180), // 180度移相的DCM时钟输出

.CLK270(CLK270), // 270度移相的DCM时钟输出

.CLK2X(CLK2X), // DCM模块的2倍频输出

.CLK2X180(CLK2X180), // 经过180度相移的DCM模块2倍频输出

.CLK90(CLK90), // 90度移相的DCM时钟输出

.CLKDV(CLKDV), // DCM模块的分频输出,分频比为CLKDV_DIVIDE

.CLKFX(CLKFX), // DCM合成时钟输出,分频比为(M/D)

.CLKFX180(CLKFX180), // 180度移相的DCM合成时钟输出

.LOCKED(LOCKED), // DCM锁相状态输出信号

.CLKFB(CLKFB), // DCM模块的反馈时钟信号

.CLKIN(CLKIN), // DCM模块的时钟输入信号

.RST(RST) // DCM 模块的异步复位信号

);

// 结束DCM_BASE模块的例化过程

在综合结果分析时,DCM系列原语的RTL结构如图3-36所示。

图3-36 DCM模块的RTL级结构示意图

Spartan-3 DCM的兼容性 DCM 输入时钟的限制 LOCKED信号的行为方式 RST 信号——重启锁定 DCM 生成向导

S3 的DCM和 Virtex-II 以及pro的DCM 功能基本相同。但是S3 DCM的技术属于3代技术,因此在抗噪性能、相移能力方面有进一步提高。(客观的说,对我们的普通应用,不是特别重要。)

但是和Spartan-2系列相比,有很大改进。S2系列不叫DCM叫DLL,可见DFS和PS等功能完全是新加入的,所以S2系列其实除了二倍频几乎没有倍频和分频能力。从这点来讲,S3真的是用起来很爽了。

和所有物理器件一样,DCM的工作范围也是受限的。由于DLL和DFS的要求各不相同,因此DCM的输入频率的限制也视乎是否同时使用DLL和DFS还是单独使用其中之一。如果同时使用,则取限制较严格者作为整个DCM系统的限制。我们来看两者的独立限制。

呵呵,这部分内容不用记哦,需要的时候查一下软件或者手册就可以了。只要明白“CLKIN输入频率有限制,而且DLL、DFS同时使用时取其严格者” 这些道理就可以了。

除了时钟限制之外,对于时钟的质量也有一定限制,主要有3个:

1. CLKIN cycle-to-cycle jitter:约束了前后两个CLKIN周期的差异;

2. CLKIN period jitter:约束了100万个cycle中最大周期和最小周期之间的差异;

3. CLKFB path delay variation:约束了从外部进来的反馈回路的延迟波动,这种延迟波动在概念上其实和jitter如出一辙。

具体数值请查手册,知道有这么回事就可以了。

LOCKED信号用于指示整个DCM系统已经和CLKIN同步,从LOCKED信号有效开始,输出时钟才可以使用,在此之前,输出时钟可能会处于各种复杂的不稳定状态。我们来看一下LOCKED信号的行为状态机。

FPGA配置:

if (CLKIN已经稳定) next_state = 判断同步;

else next_state = RST_DCM;

判断同步:

if (已经同步) next_state = 判断同步;

else next_state = 同步失败;

同步失败: next_state = RST_DCM;

RST_DCM: next_state = FPGA配置;

现在来看看各个状态下的输出。

case (state)

FPGA配置: LOCKED = 0;

判断同步: LOCKED = 1;

同步失败: LOCKED = 0;

RST_DCM:LOCKED = 0;

endcase

RST信号用于在时钟不稳定或者失去锁定时,将DCM的相关功能重置,从而重新启动锁定追踪。

作为一个输入信号,RST无法被DCM自身置位,因此需要我们的应用设计来控制这个RST信号,否则需将其接地。

置位RST会将延迟tap的位置置0,因此可能会产生glitch或者是duty cycle 发生变化,另外相位偏移也会重置回到默认值。

安装了ISE就能得到一系列accessories。利用其中的Architecture Wizard 我们可以生成DCM模块。生成的DCM将产生3种输出:

1. 一个例化了DCM的逻辑综合文件(采用生产商特定格式的VHDL / Verilog)

2. 一个UCF文件控制特定实现

3. 所有其他用户设置都保存到XAW(Xilinx Architecture Wizard)文件中。

接下来描述一下向导使用步骤。

1. 从ISE或者Arch wizard中启动界面;

2. 第一个页面做基本配置:路径、XAW文件名、VHDL / Verilog选择、综合工具、FPGA型号;

3. 进行General setup,一看就明白,不细说,注意一下几点:

- CLKIN source 如果选 external 则 DCM 的 CLKIN 会自动连接到 IBUFG。

- Feedback如果选 internal 则反馈来自 BUFG。

4. 高级设置

- 选择FPGA的配置过程是否包含DCM的锁定,如果是,则配置完成信号DONE将在LOCKED信号有效后方能有效。

- 选择CLKIN是否要除2。由于DCM的输入频率有限,对于过高的输入时钟通过除2使之可用。

- Deskew调整,这个选项建议在咨询xilinx工程师后再使用。

5. 时钟输出口 Buffer 设置

- 默认情况下所有输出口都链接 BUFG 全局时钟网络入口

- 由于全局时钟网络的入口有限,用户可以定制时钟输出口连接到其他类型的Buffer

- Global Buffer:进入全局时钟网络的入口Buffer,共有4个,简称BUFG

- Enabled Buffer:还是上面的4个全局时钟Buffer,但是配置为有使能信号控制,简称BUFGCE

- Clock MUX:还是上面的4个全局时钟Buffer,但是配置为 2-to-1 MUX类型,由S信号控制选出,简称BUFGMUX

- Low skew line:没有buffer了,只能使用 skew 比较小的连线

- Local Routing:连到本地,skew的要求不是很严格

- None:禁止输出

- 对于Enabled Buffer类型和Clock Mux类型,需要指定En口的名字

- 需要为输出时钟信号指定名字或者使用默认

6. 设置DFS

- 设置目标输出频率,然后按calculate,自动生成 M/D 值和 Jitter 值

- 或者手动设置 M/D 值,然后按calculate,自动生成频率和 Jitter 值

7. 最后输出所需的3种文件。