作者:张国斌

提起《高速数字设计》(黑魔书)的作者Howard Johnson,估计工程师无人不晓,此公这本书被全球公认为信号完整性天书!在中国,几乎每个硬件工程师都下载过他的这本著作,这个高速信号设计大牛30年前的还是一电视修理工,之后用了9年时间完成了从学士到硕士到博士的学历教育,他发明了语音压缩算法,参与了以太网标准的制订,我们今天享受到的高速以太网和千兆以太网都有他的功劳,作为一个高速信号权威,Howard Johnson的评论无疑决定着一个器件的应用前景,近日,Howard Johnson博士在赛灵思官网上发布的一段视频中对赛灵思的Virtex-7 HT FPGA的28Gbps串行接收器进行了演示。为什么Howard Johnson博士会对赛灵思的这款器件与如此浓厚的兴趣呢?

这段演示显示器件测试是采用了PRBS31模式,PRBS是Pseudo Random Binary Sequence的缩写,即“伪随机二进制序列”的意思。PRBS码的周期长度与其阶数有关,常用的阶数有7、9、11、15、20、23、31,也就是我们常说的PRBS7、PRBS9、PRBS11、PRBS15、PRBS20、PRBS23、PRBS31。PRBS码流的阶数越高,其包含的码型就越丰富,就越接近真实的线网环境,测试的结果就越准确。所以演示中的码流是最有挑战性的。

在演示中,Howard Johnson博士重点介绍了连接新一代CFP2 光纤模块所需的超广视角和抖动性能,也介绍了赛灵思的这款28Gbps收发器蕴含的意义,原来,这个全球首款28Gbps收发器意味着我们可以进入 100Gbps 和 400Gbps 带宽应用时代了。

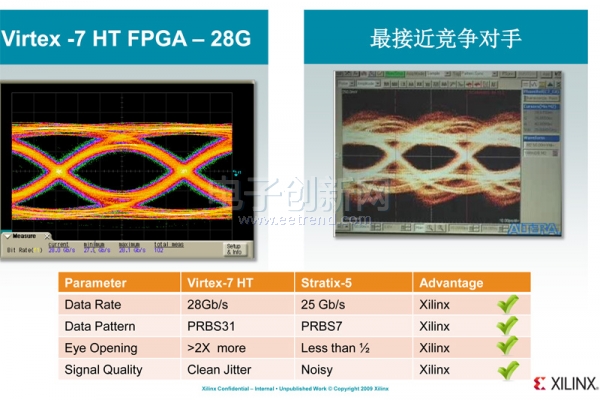

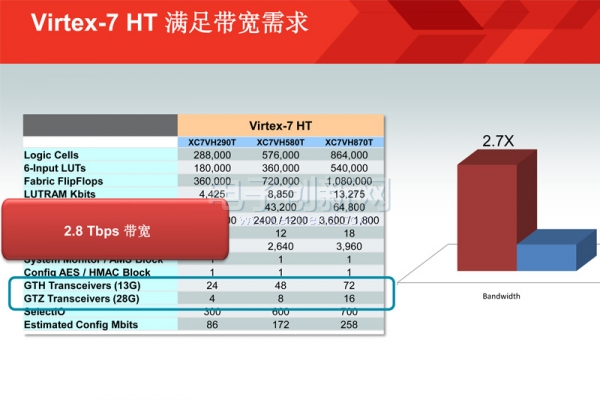

“我们5年前就在从事28Gbps收发器的开发,我们要提供一个成熟可用的产品。”近日,在赛灵思深圳Virtex-7 HT FPGA新闻发布会上,赛灵思(Xilinx)公司Serial IO高级产品市场经理Panch Chandrasekaran指出:“尽管我们的主要竞争对手在新闻稿中对外宣称其28nm FPGA实现了66个28Gbps收发器,但实际上他们至今给客户演示的28nm FPGA只有4个28Gbps收发器(而且实际性能只有25Gbps)。Virtex-7 HT系列FPGA的性能更胜一筹,28Gbps收发器数量是他们的4倍、实现总带宽是他们的2.8倍、逻辑门数是他们的1.4倍、存储器容量是他们的1.3倍。”

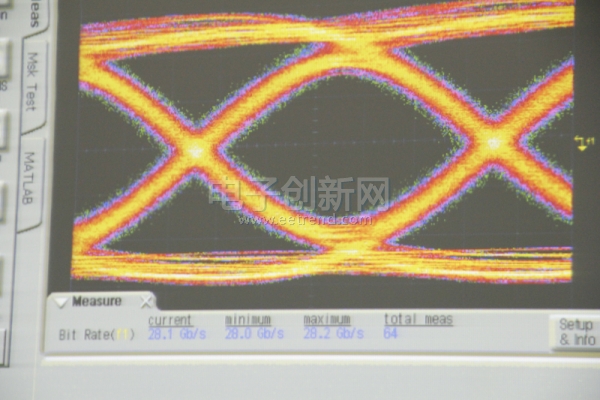

在他公布实际眼图中,我们看到,赛灵思的28Gbps收发器眼图开启的很好,学过通信人都知道,眼图的 “眼睛” 张开的大小反映着码间串扰的强弱。 “眼睛”张的越大,且眼图越端正,表示码间串扰越小;反之表示码间串扰越大。从下面两张图上可以清楚地看出两个收发器的性能差异。

赛灵思的28Gbps收发器眼图

赛灵思和竞争对手产品眼图的对比

“竞争对手产品的眼图是来源他们的网站。”为了消除我们的疑虑,Panch解释到。

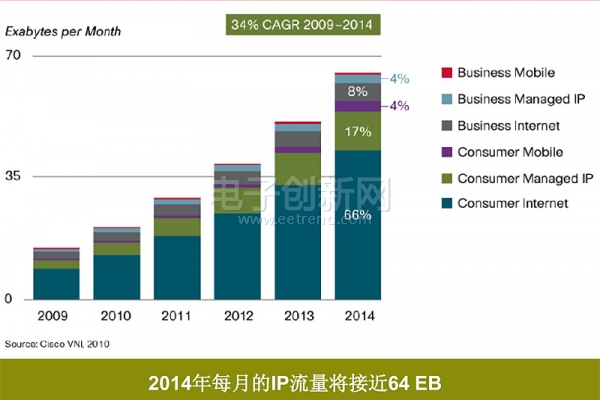

目前,个人宽带用户的平均带宽也就是2M左右,而且10Gbps应用刚刚开始,为什么赛灵思等公司会推出瞄准400G应用的带28Gbps收发器的Virtex-7 HT FPGA呢?

Panch表示这主要是全球IP流量高速增长产生的需求,据思科预计,2014 年全球 IP 流量将在 2009 年的基础上增长四倍,达到每月 64 EB,而 2009 年的月流量约为 15 EB。到 2014 年,全球年 IP 流量将达到近 0.75 ZB(767 EB)!一个ZB等于一万亿GB(供参考: 1B=8bit, ,1KB=103B,1MB=106 ,1GB=09B,1TB=1012B,1PB=1015B拍字节约等于 1015 字节,1EB=B1018艾字节约等于 1018 字节,1ZB=1021B或 1,000,000,000,000,000,000,000 字节。

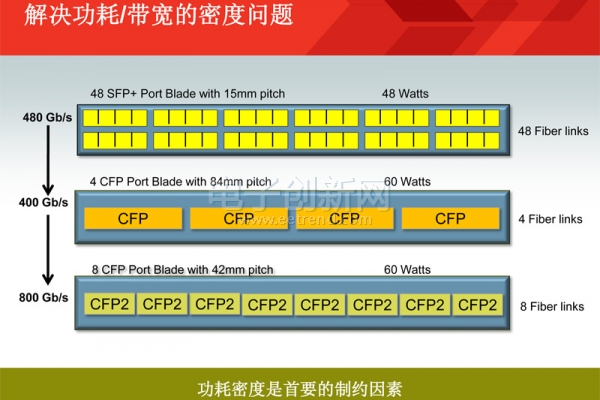

为了紧跟这一发展趋势,通信设备厂商已经在设计新一代100G-400Gbps 系统设备了,另外,为了在不扩大外型或功耗预算的情况下最大限度地提高面板带宽密度也需要更高速的收发器。Finisar公司高速光纤模块市场营销总监 Christian Urricariet 就曾表示:“为了满足日益增长的带宽需求,我们预计通信设备厂商将采用新的 CFP2 型光纤模块来设计新一代100 和 400Gbps 系统。这将最大限度地提高面板的带宽密度,同时优化现有产品的功耗预算。”

从上图中,我们就可以看功耗密度是到通信设备商要解决的首要难题,一个交换机机柜目前可提供480Gbps总带宽,它有48个SFP+端口刀片服务器,每个刀片服务器采用1个10GbE输出,此时每个刀片间隔15mm,总功耗为48W。为了加大散热间隔和减少光纤数(降低成本),在同样尺寸机柜里可以采用4个CFP端口刀片服务器,每个刀片服务器提供100GbE输出,每个CFP采用10个10GbE输入,这样可将总系统带宽提供到400Gbps,这可以将间隔减到84mm,不过这个方法提供的带宽要低于SFP+,在以更低功耗提供更高带宽方面,CFP落败了。

新兴的CFP2模组规范可以满足这个要求,CFP2和CFP的主要区别是CFP2有“变速箱”的功能,就是可以把10个10.3125G 数据流变成4个25G数据流,所以可以提高功耗密度,一个单个 CFP2 模块可以通过4个25G光纤提供100 Gbps 带宽(而间距为42mm),所以,8个CFP2模块可以提供800 Gbps带宽,而只维持了同样的60w功耗,其功耗密度比SFP+和CFP都高!

赛灵思亚太区应用市场总监张宇清表示:“赛灵思此次发布的 Virtex-7 HT FPGA有16个28Gbps和72个13.1Gbps 串行收发器,总带宽提高到2.8Tbps,这是目前业界最大带宽。”此外,他表示Virtex-7 HT FPGA系列产品很丰富,适用多种应用,例如该系列包含从290,000个逻辑单元的低成本100G“智能变速箱”芯片到包含870,000 个逻辑单元的全球首款400Gbps FPGA,其中支持100Gbps、2 x 100Gbps 或400Gbps 接口、高效连接、基于3Gbps 或6Gbps 的传统系统端接口和 10Gbps ASIC 及 ASSP 芯片等应用。这意味着 Virtex-7 HT FPGA 可用于多种应用,例如:支持 OTU-4(光传输单元)转发器、复用转发器或 SAR(业务汇聚路由器)的 100Gbps 线路卡、面向高速数据处理的低成本 120Gbps 包处理线路卡、多 100G 以太网端口桥、400Gbps 以太网线路卡、符合19.6Gbps CPRI(通用公共无线电接口)基站和远程无线电前端以及100Gbps 和400Gpbs 测试设备等等。

Virtex-7 HT FPGA总带宽提高到2.8Tbps

实际上,除了在通信领域,在其他高速信号处理领域,例如包括雷达阵列以及侦察机在内的航空航天和军用产品应用,Virtex-7 HT FPGA也可以大显身手。

张宇清表示技术发展表明,到2012年,100-400Gbps应用已经逐渐成熟,从光模块到相应的标准都已经成熟。“所以,XilinxVirtex-7 HT 拥有28G 生态系统的支持,现在,很多电信设备商已经设计好了产品,这些都预留了光模块的位置,届时,插入光模块就可以跨入100-400Gbps时代了。”

XilinxVirtex-7 HT 拥有28G 生态系统的支持

Panch表示其实要实现28Gbps收发器的挑战非常巨大,首当其冲是要解决系统抖动问题,对此,赛灵思采取的措施有:

1、提供满足CEI-28G标准的低相位噪声谐波锁相环

2、在FPGA上有具自动调准功能的信号调整电路;

3、有专门的噪音分离架构,这可以可将模拟和数字电路之间的噪音耦合减少5-10db。

实现系统级抖动

所以,好产品不是说出来的而是精心设计出来的,我想,这也是这个产品可以赢得Howard Johnson博士青睐的主要原因!

如欲观看该演示视频,请访问: http://www.xilinx.com/28gbps 。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网