1 引言

随着数字信号处理技术的不断发展,大容量可编程逻辑器件的不断涌现,FPGA技术越来越多地应用在大规模集成电路设计中。在此硬件系统设计中,经常会遇到需要大容量的数据存储的情况,下面我们将针对FPGA中内部Block RAM有限的缺点,提出了将FPGA与外部SRAM相结合来改进设计的方法,并给出了部分VHDL程序。

2 硬件设计

这里将主要讨论以Xilinx公司的 FPGA(XC2S600E-6fg456)和ISSI公司的SRAM(IS61LV25616AL)为主要器件来完成大容量数据存储的设计思路。

FPGA即现场可编程门阵列,其结构与传统的门阵列相似,大量的可编程逻辑块(CLB, Configurable Logic Block)在芯片中央按矩阵排列,芯片四周为可编程输入/输出块(IOB, Input/Output Block),CLB行列之间及CLB和IOB之间具有可编程的互连资源(ICR, Inter Connect Resource)。CLB、IOB和ICR都由分布在芯片中的SRAM静态存储单元控制,SRAM中的数据决定FPGA的功能,这些数据可以在系统加电时自动或由命令控制从外部存储器装入 。

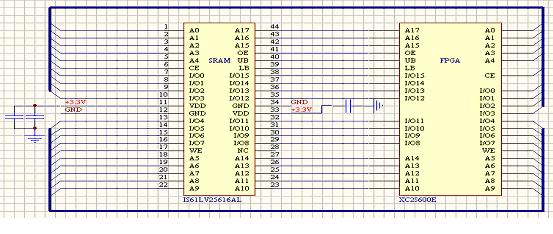

在进行数据存储时,可直接将数据写入FPGA内部的Block RAM中,在一定程度上减少了FPGA的资源分配。但FPGA内部自带的RAM块毕竟是有限的,当需进行大容量数据存储时这有限的RAM块是远远不能满足系统设计要求的。此时,就需要将FPGA与外部RAM相结合完成大容量数据存储。具体硬件电路如图一所示:

图一 硬件电路原理图

3 IS61LV25616AL功能简介

IS61LV25616AL是Integrated Silicon Solution 公司(ISSI)的一款容量为256K×16的且引脚功能完全兼容的4Mb的异步SRAM,可为Xilinx公司的Spartan-2E系列FPGA提供高性能、高消费比的外围存储。除了256K×16异步SRAM外,ISSI还提供128K×16、512K×16、256K×8、512K×8和1M×8的异步SRAM。

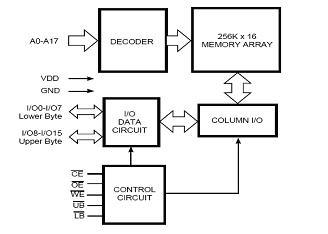

IS61LV25616AL引脚结构框图如图二所示:

图二 IS61LV25616AL结构框图

3.1主要特征

(1)工作电压:3.3伏;

(2)访问时间:10ns、12ns;

(3)芯片容量:256K×16;

(4)封装形式: 44引脚TSOPII封装,也有48引脚mBGA和44引脚SOJ封装;

(5)采用0.18μm技术制造;

3.2引脚功能

(1)A0~A17:18位的地址输入线;

(2)IO0~IO15:16位的三态数据输入输出线;

(3) :写控制线;

(4) : 片选信号;

(5) :输出使能信号;

(6) 、 :低字节、高字节使能信号;

(3)~(6)的控制线均为低电平有效。

3.3控制逻辑电路设计

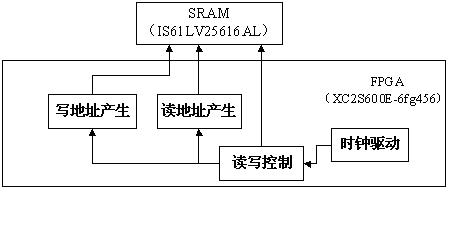

如图三所示,控制逻辑由FPGA来实现。主要包括读地址产生器、写地址产生器、读写时钟信号产生器及读写控制等几部分。下面分别加以讲述。

图三 原理框图

(1)写地址产生器:由于设计时采用256K×16 的SRAM,故有18位地址,写地址产生器用18位计数器实现。靠外部时钟驱动,每进行一次写操作后,读写控制单元产生计数脉冲,使其增1,直到18位计数器计满再循环写入地址为0的空间。

(2)读地址产生器同上,也采用18位计数器实现,根据系统要求,每隔一定的采样周期将读地址指针偏移一定偏移量,并从该位置读取数据。

(3)读写地址选择器由于读写地址复用管脚,因此在读写操作时,必须选通相应的地址。这就需要由FPGA控制芯片上的 、 、 、 等控制信号来对SRAM进行读写的操作。

(4)此外,由于读写之间的切换,数据线上的数据在切换瞬间如不加处理会出现混乱现象。因此,为避免读、写操作发生冲突,数据线呈三种状态,读数据、写数据及高阻态。在从写到读的过程中需给数据线上送高阻态。

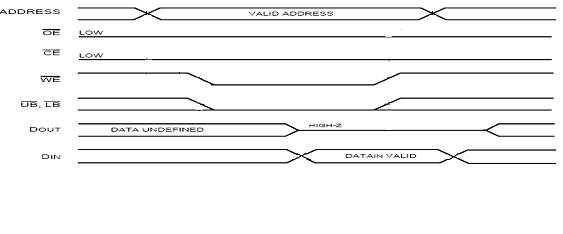

(5) 当需要对SRAM进行写操作时,由FPGA控制产生写地址选通信号,该选通信号为一单脉冲形式,如图四中 、 、 ,该脉冲下降沿触发SRAM,告知开始对RAM进行写操作,使FPGA输出写地址,同时给数据线上送数据。在写操作期间, 、 片选信号始终保持低电平,而写地址选通信号上升沿到来时使写地址计数器增1。以此类推,通过写地址选通信号高低电平变化完成对数据依次写入。需要注意的是,地址线和数据线在 、 、 为高时可同时赋新值,但只有在 变低后赋予数据线上的新值才有效。  图四 RAM写操作时序

图四 RAM写操作时序

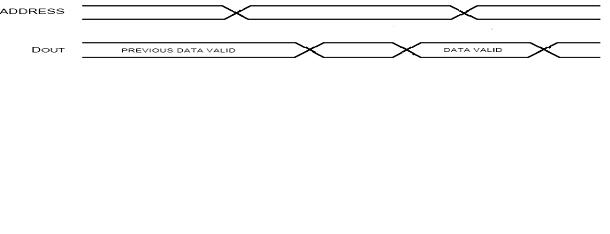

对SRAM进行读操作相对较简单,在进行读操作期间, 、 、 、 始终为低电平, 始终为高电平。每进行一次读操作,地址按系统要求变化一次。同时注意,地址的变化时刻总要先于数据的变化时刻。图五为RAM读操作时序。

图五 RAM读操作时序

以下是一段用VHDL语言描述的控制RAM的读写操作时序的程序代码:

OE_SRAM<=LOWLEVEL;

CE_SRAM<=LOWLEVEL;

when 0 => addr_SRAM<=temp_addr_SRAM; --WRITE to SRAM

data_SRAM<=data_in;

WE_SRAM<=‘1‘;

LB_SRAM<=‘1‘;

UB_SRAM<=‘1‘;

when 1 => WE_SRAM<=‘0‘;

LB_SRAM<=‘0‘;

UB_SRAM<=‘0‘;

when 2 => WE_SRAM<=‘1‘;

LB_SRAM<=‘1‘;

UB_SRAM<=‘1‘;

when 3 => WE_SRAM<=‘1‘; --READ from SRAM

LB_SRAM<=‘0‘;

UB_SRAM<=‘0‘;

data_SRAM<=b"ZZ_ZZZZ_ZZZZ_ZZZZ_ZZZZ"; --给数据线上送高阻

addr_SRAM<=temp_addr_SRAM;

when 4 => data_out <=data_SRAM;

程序中,在进行读写操作时,片选使能信号CE_SRAM及输出使能信号OE_SRAM始终为低电平。

· 第0时刻到第2时刻在进行写操作:第0时刻地址线addr_SRAM和数据线data_SRAM同时赋新值,控制线WE_SRAM 、LB_SRAM、 UB_SRAM要经历一个窄脉冲的变化过程, RAM在获取到此控制线下降沿信息后,便知开始进行写操作。需要注意的是,虽然数据在第0时刻已赋到数据线上,但因为写操作是控制线低电平有效,所以数据线上真正发生数据更新是在控制线变为低电平之后,因此,数据线上的实际更新时刻是在第2个时刻。

·第3、4状态是进行读操作:在读写转换时刻,也就是在第3时刻如前所述需给数据线上送高阻态。这样,读取数据的时序关系由系统时钟进行控制,在第3时刻给地址线上送要读取的地址,第4时刻将数据端口上的数据送出。这里需注意的是,读取数据要比读取地址晚一个时刻。从而,完成了对外部RAM的读写操作控制。

4结论

该系统已应用在罗兰—C导航接收机的信号处理中。实验证明,此设计可靠稳定地完成了大容量高速异步数据存储,进一步提高了系统的性能。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网