1 FIR滤波器原理

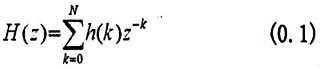

有限冲激响应(FIR)数字滤波器和无限冲激响应(IIR)数字滤波器广泛应用于数字信号处理系统中。IIR数字滤波器方便简单,但它相位的非线性,要求采用全通网络进行相位校正,且稳定性难以保障。FIR滤波器具有很好的线性相位特性,使得它越来越受到广泛的重视。FIR数字滤波器是一个线性时不变系统(LTI),N阶因果有限冲激响应滤波器可以用传输函数H(z)来描述,

在时域中,上述有限冲激响应滤波器的输入输出关系如下:

其中,x[n]和y[n]分别是输入和输出序列。

N阶有限冲激响应滤波器要用N+1个系数描述,通常要用N+1个乘法器和N个两输入加法器来实现。乘法器的系数正好是传递函数的系数,因此这种结构称为直接型结构,可通过式(1.2)来实现。

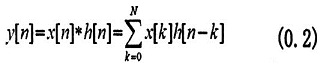

当冲击响应满足下列条件时,FIR滤波器具有对称结构,为线性相位滤波器:

![]()

这种对称性,可使得乘法器数量减半:对n价滤波器,当n为偶数时,乘法器的个数为n/2个;当n为奇数时,乘法器的个数为(n+1)/2个。在电路实现中,乘法器占用的逻辑单元数较多。乘法器的增加,意味着电路成本增加,另外对电路的工作速度也有影响。

N阶线性相位的因果FIR系统的单位冲激响应滤波器可用对称冲激响应

来描述。

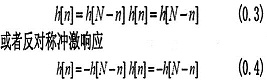

具有对称冲激响应的FIR传输函数的冲激响应可写成如下形式:

当N为偶数时

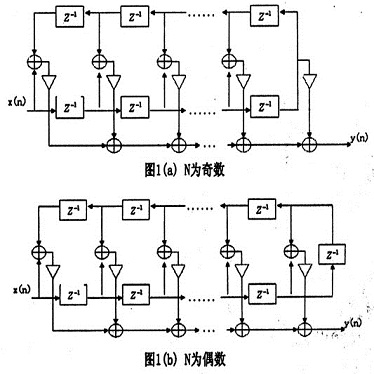

则FIR线性相位系统的结构可转化成如图1(a)和图1(b)所示。

2 滤波器设计方案

随着数字技术日益广泛的应用,以现场可编程门阵列(FPGA)为代表的ASIC器件得到了迅速普及和发展,器件集成度和速度都在高速增长。FPGA既具有门阵列的高逻辑密度和高可靠性,又具有可编码逻辑器件的用户可编程特性,可以减少系统设计和维护的风险,降低产品成本,缩短设计周期。

分布式算法是—种以实现乘加运算为目的的运算方法。它与传统算法实现乘加运算的不同在于执行部分积运算的先后顺序不同。简单地说,分布式算法在完成乘加功能时是通过将各输入数据每一对应位产生的部分积预先进相加形成相应部分积,然后在对各部门积进行累加形成最终结果,而传统算法是等到所有乘积产生之后再进行相加来完成乘加运算的。与传统算法相比,分布式算法可极大地减少硬件电路规模,很容易实现流水线处理,提高电路的执行速度。

FPGA有着规整的内部逻辑块阵列和丰富的连线资源,特别适合细粒度和高并行度结构特点的数字信号处理任务,如FIR、FFT等。利用FPGA实现FIR滤波器的设计过程,并且对设计中的关键技术一分布式算法进行详细描述。

FIR滤波器的结构主要是非递归结构,没有输出到输入的反馈。并且FIR滤波器很容易获得严格的线性相位特性,避免被处理信号产生相位失真。而线性相位体现在时域中仅仅是h(n)在时间上的延迟,这个特点在图像信号处理、数据传输等波形传递系统中是非常重要的。此外,他不会发生阻塞现象,能避免强信号淹没弱信号,因此特别适合信号强弱相差悬殊的情况。

通常采用窗函数设计FIR滤波器方法简单,但是这些滤波器的设计还不是最优的。首先通带和阻带的波动基本上相等,另外对于大部分窗函数来说,通带内或阻带内的波动不是均匀的,通常离开过渡带时会减小。若允许波动在整个通带内均匀分布,就会产生较小的峰值波动。对于线性相位因果FIR滤波器,它的系列具有中心对称特性,即h(i)=±h(N一1一i)。令s(i)=x(i)±x(N一1一i),对于偶对称,代入式(1)可得:

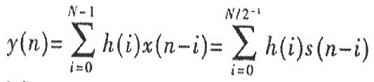

根据要求,要设计一个输入8位,输出8位的9阶线性相位FIR滤波器,所以采用图2(a)的方式,其中输入信号范围为:[99,0,0,O,99,O,0,0,99,O,0,0,99,…],此滤波器Fs为lOOkHz,Fc为10kHz。利用MATLAB设计计算9阶FIR滤波器系数和幅频响应如下:

整数化后,可得FIR滤波器的参数为:[4c,4f,50,52,52,52,50,4f,4c:]

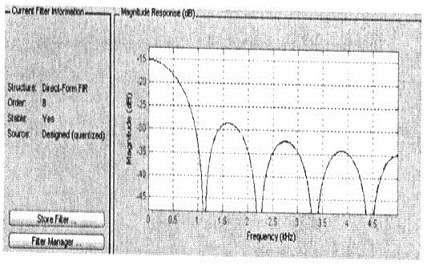

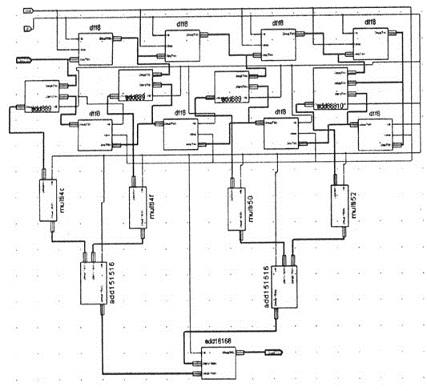

根据以上所说的思路,可以将FIR滤波器的原理图设计如下:

下面对各加法器乘法器的输出位数进行分析,对第一级加法器,输入为8位,输出统一为9位,最后一个加法器为三输入端,输入都为8位,输出为10位。对各个乘法器进行分析,第一个乘法器为4c,因此输入为9位,输出为15位。第二个乘法器为4f,输入为9位,输出为15位。第三个乘法器为50,输入为9位,输出为15位。第四个乘法器为52,输入为10位,输出为16位。乘法器输出结果两两相加,第一个加法器输入都为15位,输出为16位,第二个加法器,输入分别为15位和16位,输出为16位。最后这两路输出之和为16位。将后8位舍去,然后相加,总输出为8位。至此,所有器件的输入输出都已经判定。下面进入模块设计阶段。

3 模块设计

设计的FIR滤波器由10个小VHD文件和一个总体BDF文件组成,VHD文件可以分为以下三种模块:寄存器、加法器、乘法器。

3.1 寄存器设计

寄存器用于寄存一组二值代码,对寄存器的触发器只要求它们具有置1、置0的功能即可,因而本设计中用D触发器组成寄存器,实现寄存功能。

在CP正跳沿前接受输入信号,正跳沿时触发翻转,正跳沿后输入即被封锁。

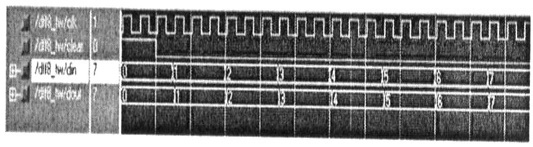

寄存器的波形仿真

3.2 加法器

在将两个多位二进制数相加时,除了最低位以外,每一位都应该考虑来自低位的进位,即将两个对应位的加数和来自低位的进位3个数相加。这种运算称为全加,所用的电路称为全加器。

实现两个二进制数字的相加运算。当到达时钟上升沿时,将两数输入,运算,输出结果。

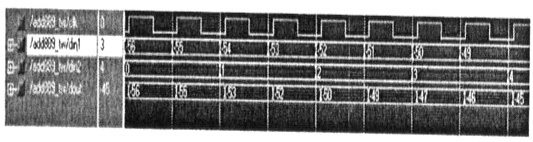

加法器的波形仿真

3.3 乘法器

从资源和速度考虑,常系数乘法运算可用移位相加来实现。将常系数分解成几个2的幂的和形式。下例为乘4c电路设计。实现输入带符号数据与固定数据两个二进制数的乘法运算。当到达时钟上升沿时,将两数输入,运算,输出结果。

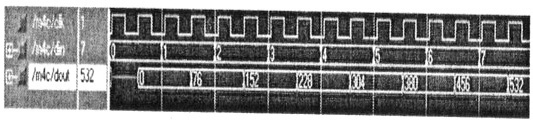

乘法器的波形仿真

4 FIR滤波器整体电路

FIR滤波器的整体电路基本与其原理图类似。整体电路如下图所示:

5 FIR滤波器整体电路仿真结果

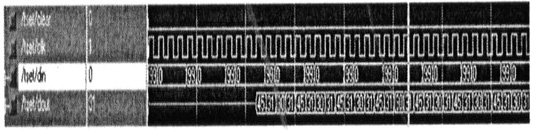

当输入为信号为[99,0,0,0,99,0,0,0,99,O,0,0,99。…]滤波器的实际仿真波形见下图:

因为该滤波器为九阶,信号通过各级触发器,加发器乘法器的总延迟为13个时钟周期,故在仿真中前13个时钟周期没有信号输出。通过matl ab对滤波器进行仿真得出的理论输出序列为:[33,28,34,50,33,28,34,50,33,28,34,50,33,28,34,50…….]与实际仿真波形比较,波形基本一致,但是因为该滤波器只有九阶,所以与理论值有一定误差。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网