引 言

电动机是各类数控机床的重要执行部件。要实现对电动机的精确位置控制,转子的位置必须能够被精确的检测出来。光电编码器是目前最常用的检测器件。光电编码器分为增量式、绝对式和混合式。其中,增量式以其构造简单,机械寿命长,易实现高分辨率等优点,已被广泛采用。增量式光电编码器输出有A,B,Z三相信号,其中A相和B相相位相差90°,Z相是编码器的“零位”,每转只输出一个脉冲。在应用中,经常需要对A相、B相正交脉冲按照一定的比例,即分周比进行分频。分频的难点是,无论设定分周比是整数还是分数,分频后输出的A'相,B'相脉冲仍然要保持正交或近似正交。为此提出一种基于FPGA的整数分周比实现方法。该方法逻辑结构简单,配置灵活,易于扩展,具有很高的实用价值。

1 电子齿轮比与分周比

电子齿轮比与分周比是数控机床和数控加工中心中一个很重要的概念。国外大部分伺服驱动装置有电子齿轮比和分周比功能,其中电子齿轮比KEG为伺服电机实际执行的脉冲量与指令脉冲量之比,分周比KDF是伺服驱动器接收到来自伺服电动机轴上脉冲编码器的脉冲量与实际反馈到上位伺服控制系统(CNC)上脉冲量的比。配合使用电子齿轮比和分周比功能,用户可以方便地实现整数脉冲当量,从而避免中间计算出现量化误差,在不修改G代码的情况下,将代码直接移植到配备不同电机编码器线数或者不同螺距丝杠的机床或者加工中心。

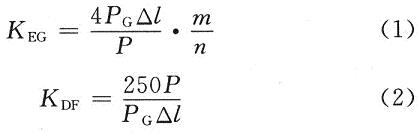

电子齿轮比和分周比可以按照下式计算求得。

式中:PG为电机光电编码器线数,单位为P/rev(脉冲/转);P为丝杠螺距,单位为mm/rev(毫米/周);△l为脉冲当量,单位为mm/P(毫米/脉冲);m/n为减速比。

电子齿轮比可以利用脉冲频率的变换实现,而对于分周比,由于驱动器反馈到CNC的脉冲量一般采用正交脉冲序列,故分周比的实现相对于齿轮比要困难。国外的各种驱动器一般都带有分周比功能,对利用FPGA实现分周比进行研究和探讨,电子齿轮比、分周比功能示意图如图1所示。

2 分周比的原理框图

分周比功能的实现结构如图2所示。

分周比的实现需要3个功能模块:四倍频模块QD-PF、分频模块DF、正交序列生成模块OSG。QDPF模块的输入为正交脉冲序列,输出为方向信号和四倍频后的脉冲。DF模块可实现输入脉冲的三分频。DF内部是一个增减计数器,根据输入的方向信号进行增、减计数,正向计至设定的正阈值后输出一个脉冲和正方向信号,负向计至设定的负阈值后输出一个脉冲和负方向信号。当计数值在正负阈值之间时,即使电机方向发生变化,甚至抖动,输出方向信号都保持不变。

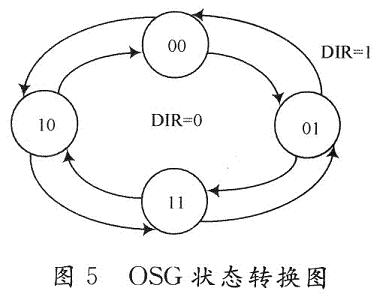

OSG模块用输入脉冲沿触发内部状态机进行状态转换,根据输入的方向信号判决要跳转的状态,从而产生正交信号和方向信号。

3 仿真研究

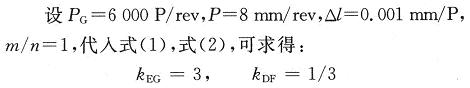

根据图2,利用ACTEL公司的Libro 8.1开发平台,采用VHDL硬件语言,创建了相应的功能模块,原理图如图3所示。

图3中,PA205,PB206分别是原始差分信号的A相、B相的输入引脚。信号经QDPF四倍频后将方向信号和脉冲信号输出给DF分频模块。经DF分频后将脉冲、方向信号输出给正交脉冲生成模块OSG,产生带相位的正交信号,最后从PA119,PB120反馈到CNC。下面对主要模块做分别介绍。

四倍频模块QDPF:正交信号的四倍频方法有很多种,在很多资料中都涉及,在此不做详细介绍。

分频模块DF按照初始化配置的分周比或者预先设定的分周比,对输入CLK_IN引脚的脉冲序列分频。内部的增、减计数器根据输入DIR_IN引脚的方向信号对输入脉冲进行增(DIR_IN=1)或减(DIR_IN=0)计数,增计数至正阈值时输出一个脉冲和正方向信号(DIR_OUT=1),减计数至负阈值是输出一个脉冲和负方向信号(DIR_OUT=0)。若计数值在正、负阈值之间时,不论电机反向,还是在阈值见抖动,即方向反复变化,输出方向信号都保持不变。这是能正确实现分频的关键,如果这一步处理不好,电机定位后可能会出现不断向CNC发脉冲的情况。以三分频为例,即计数器增计数至3后输出一个正脉冲(正方向信号+脉冲),计数器减计数至-3后输出一个负脉冲(负方向信号+脉冲)。计数值在(-3,3)时,计数器只对脉冲计数而不输出。对QDPF 的仿真结果如图4所示。

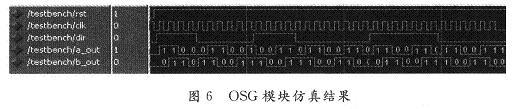

OSG被脉冲信号的上升沿触发后,根据当前状态和方向信号,跳到下一个状态。当方向信号为正时,按照外环的逆时针方向切换状态,产生A'相超前B'相 90°的正交脉冲序列;当方向信号为负时,按照内环的顺时针方向切换状态,产生B'相超前A'相90°的正交脉冲序列,仿真如6所示。

图6中,dir为方向信号,其跳变沿即方向变化处。由图6可见,电机正转时顺序为10→11→01→00(反向)→01→11→10→…。实现了相位随输入信号的切换。

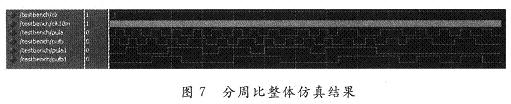

最后,对分周比功能整体结构进行仿真,输入为正交的脉冲序列。输入模仿实际电机光电编码器脉冲输出对脉冲相位反复切换以验证电机定位后的输出。仿真如图7所示。

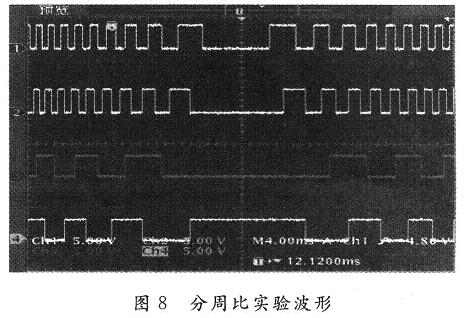

从图7中可见,当输入信号pula,pulb相位不断切换时,输出pula1,pulb1按照3分频,满足3或-3后输出新的正交序列。实际实验波形如图8所示。

图8中,波形1、波形2分别是光电编码器输出的A相、B相正交脉冲。波形3、波形4分别是对A相、B相正交脉冲3分频后的A'相、B'相正交脉冲。观察图 7,图8,结果一致。用此方案实现的分周比已经成功应用于高精度伺服驱动器中,在实际应用中反复验证,未发现误差。

4 结 语

本文提出的分周比实现方法可以准确地将光电编码器输出的正交信号按照设定的分周比进行分频。通过设定分频比可以实现1~256倍的分频,甚至更高。在实际系统中,还可以利用MCU通过总线在线配置分周比。假如要实现分数比例的分周比,也只需在本方案基础上稍加改进即可。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网