PXI总线是NI公司在计算机外设总线PCI的基础上实现的新一代仪器总线,已经成为业界开放式总线的标准,基于PXI总线的数字化仪模块是现代测试系统中重要的一种数据记录与处理设备。设计一个双通道12 bit/250 MHz采样频率的高速数字化仪模块,以高性能FPGA器件为核心,实现对高速A/D的控制以及高速数据处理和存储,解决了长时间高速记录信号的测试难题。

1 系统工作原理

数字化仪模块主要由前端信号调理通路、模数转换电路、数据存储单元、数据采集控制电路、PXI接口电路等部分组成,其原理框图如图l所示。

高速

2 系统设计实现

2.1 模块化的FPGA设计

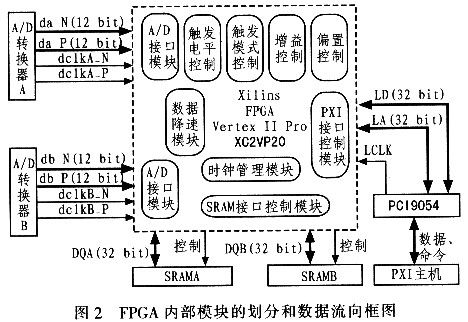

本文所设计的数字化仪是基于高性能FPGA芯片实现的,FPGA承担了绝大部分的控制和数据处理任务,是本设计的核心器件。对FPGA进行模块化设计,是大型系统设计的常用方法。合理分割功能模块,能加快FPGA的开发,也有利于代码的移植和重复利用。在设计时将FPGA分成高速A/D接口模块、数据降速模块、调理通路控制模块、存储接口模块、PXI接口控制模块等主要功能模块设计。FPGA内部模块划分和数据流向如图2所示。

A/D接口模块主要实现FPGA和高速A/D转换器的互联,以LVDS格式总线接收数据和采样时钟,该部分电路决定数据采集的稳定性,需要从硬件和软件两个方面保证;数据降速模块采用抽取滤波器将信号降低到需要的采样速率;调理通路控制模块主要实现对A/D前端电路的控制,包括耦合方式、匹配阻抗选择、增益自动控制、偏置和触发电平控制等;PXI接口部分主要实现和PXI主机的通讯译码;存储控制模块完成对外部SRAM的控制,实现数据缓存;时钟管理模块负责采样时钟的分频、倍频等处理。

2.2 高速数据采集和存储接口设计

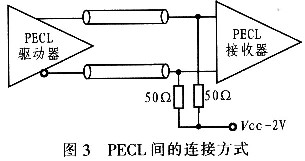

高速数据采集系统的输入输出接口设计是尤为重要的,高速IC芯片的相互连接是决定数据采集系统稳定性的关键因素之一,低功耗及高的信噪比是有待解决的主要问题。通常实现高速采集系统中芯片间互联有两种接口:PECL和LVDS。正电压射极耦合逻辑PECL(Positive Emit-ter-Coupled Logic)信号的摆幅小,适合于高速数据的串行或并行连接,PECL间的连接一般采用直流耦合,输出设计为驱动50 Ω负载至(VCC -2V),连接电路如图3所示。

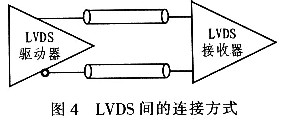

低压差分信号LVDS(Low Voltage Differential Signal)标准是一种小振幅差分信号技术,它使用非常低的幅度信号(100~450 mV)。通过一对平行的PCB走线或平衡电缆传输数据。在两条平行的差分信号线上流经的电流方向相反,噪声信号同时耦合到两条线上,而接收端只关心两信号的差值,于是噪声被抵消。由于两条信号线周围的电磁场也互相抵消,故差分信号传输比单线信号传输电磁辐射小很多,从而提高了传输效率并降低了功耗。LVDS的输入与输出都是内部匹配的,采用直连方式即可,连接方式如图4所示。

本设计中。A/D转换器选用Mamix公司的MAXl215,该芯片是一款12 bit/250 Ms/s的高速A/D转换器,它具有出色的SNR和SFDR特性,使用250 MHz差分采样时钟,接收差分输入信号,输出12位LVDS格式的差分数字信号,提供差分同步时钟信号。为了提高测试精度,单端的输入信号需要转换成差分模式后再送入A/D,增益调整及单端到差分转换电路的局部如图5所示。考虑阻抗匹配问题,在单端信号转换为差分模式时,需要在2个差分线上串联50 Ω的匹配电阻,作为LVDS信号的发送端。

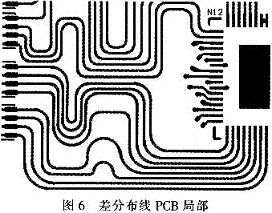

在PCB的设计中,对差分线要进行特别处理。差分线在走线区间内的实际布线公差应控制在5 mil内;差分对内两条线之间的距离应尽可能小,以使外部干扰为共模特征;要保证每个差分对内的长度相互匹配,以减少信号扭曲;采用电源层作为差分线的信号回路,因为电源平面有最小的传输阻抗,可以有效减少噪声影响。图6所示为本设计PCB的局部。

本设计中FPGA作为LVDS信号的接收端,首先需要将A/D输入的LVDS差分数据和同步时钟信号转换成单信号。此处选用了xilinx公司的VirtexⅡ-Pro系列FPGA,该系列的FPGA嵌入了高速I/O接口,能实现超高带宽的系统芯片设计,支持LVDS、LVPECL等多种差分接口,适应性很强,为高速数据接口提供了完善的解决方案。LVDS差分信号的接收可以通过例化IBUFDS_LVDS这个模块来实现,同时在程序中设置使用内部的匹配电阻,实现LVDS的阻抗匹配。差分时钟信号由全局时钟输入脚接入FPGA,然后通过调用xFPGA特有的数字时钟管理模块(DCM),将时钟转换成单信号并进行分频、移相等处理,作为后续处理的时钟信号。

2.3 PXI接口设计

PXI是PCI在仪器领域的扩展(PCI eXtensions for Instrumentation),它将CompactPCI规范定义的PCI总线技术发展成适用于试验、测量与数据采集场合应用的机械、电气和软件规范,从而形成了新的虚拟仪器体系结构。PXI模块化仪器系统具备高速的性能,并与PCI保持兼容性,形成一种主流的虚拟仪器测试平台。本设计中使用PCI9054进行PXI接口硬件的设计,PCI9054是美国PLX公司生产的一款32位/33 MHz通用PCI总线控制器专用器件,它具有强大的功能和简单的用户接口,为PCI总线接口的开发提供了一种简便方法。

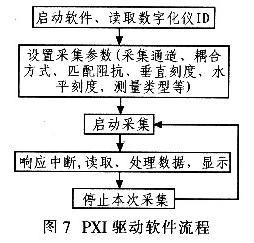

2.4 PXI驱动开发

PXI的软件要求包括支持Microsoft Windows NT和95(WIN32)这样的标准操作系统框架,要求所有仪器模块带有配置信息(configuration information)和支持标准的工业开发环境(如NI的LabVIEW、LabWindows/CVI和Microsoft的VC/C++、VB和Borland的C++等),而且符合VISA规范的设备驱动程序(WIN32 device drivers)。本设计应用K

3 结束语

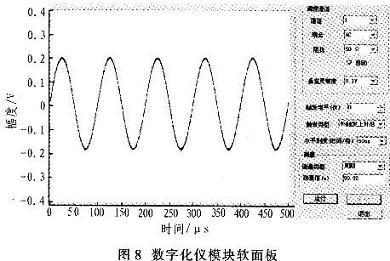

本文给出了基于PXI总线接口的高速数字化仪模块的设计实现方法,介绍了高速数据采集系统中LVDS接口、LVPECL接口电路结构及连接方式,并在所设计的数字化仪模块中得到应用。系统可以稳定的工作在250 MHz,实现高精度、长时间的数据采集和分析。该数字化仪模块已成功应用于多个PXI测试系统中,广泛应用于工业自动化、通信、科研、军事、航空航天、消费电子等多个领域。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网