不管是放到测试设置中,还是作为被测设备的一部分,时钟恢复都在进行准确的测试测量时发挥着重要作用。由于大多数千兆位通信系统都是同步系统,因此系统内部的数据都使用公共时钟定时。不管是沿着几英寸的电路板传送,还是经过光纤横跨大陆,数据与其定时输入的时钟之间的关系都可能会被打乱。通过直接从数据中提取时钟,可以在接收机正确实现信号再生。

必须指出的是,接收机通常会改善输入的数据信号,然后再继续传送。接收机中的判定电路对数据再定时,使波形变方。这一过程依赖于与输入数据同步的时钟信号。接收机内部的时钟恢复功能实现了这一目标,前提是再定时时钟要以相同的方式、相同的时间移动。

基于PLL的时钟恢复

可以通过不同架构实现时钟恢复,测量设备中最常用的是基于锁相环(PLL)的方法。根据在数据中看到的跳变,使用恢复电路导出与输入数据同步的时钟,这取决于看到数据中的跳变。对拥有多串完全相同位的数据段,PLL必须保持锁定。环路增益对环路带宽的影响最明显,环路滤波器内部的任何滤波一般都会产生次生效应。应该指出的是,输入数据的跳变密度会影响进入环路的能量,进而影响环路的特性。因此,一致性测试中的环路带宽会视选择的码型的跳变密度而变化。

系统转函在输入信号的相位调制上执行低通滤波操作,错误响应转函则执行高通滤波功能。在未能追踪带宽以外的相位调制时,环路会追踪环路带宽以内的输入相位调制。这样,环路就可以追踪低频抖动,而忽略PLL环路带宽以外的高频抖动。

衡量PLL抖动追踪特性的指标之一是环路带宽(LBW),通常在“抖动输入/抖动输出”转函为-3dB的点上测得。但这并不是确定环路的唯一方式。

宽LBW改善了抖动容限,窄LWB则会从被恢复的时钟中去掉更多的抖动,这有利于下游的同步器,但会降低抖动容限。尽管宽LBW似乎是理想选择,但通常还要考虑成本和技术。宽LBW还会带来更多的噪声或随机抖动。目前测量中使用的LBW一般在1~10MHz的范围内。

时钟恢复的输入和输出

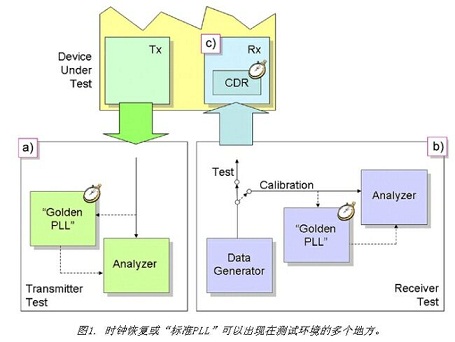

必须指出测量中是怎样使用时钟恢复的,哪些地方会发生错误。例如,在发射机测试一侧,要求时钟恢复的主要原因通常有两个:没有提供作为测试设备触发的时钟信号,或者标准要求使用特定的LBW进行抖动测量(参见图1中的a部分)。后一种情况的目的,是用系统接收机(如BERTScope BSA系列)包含时钟恢复来追踪部分输入抖动,这样发射机测试应该只涉及接收机没有追踪的高频抖动(参见图1)。

由此可见,对抖动成分接近时钟恢复LBW的被测信号,LBW设置不正确可能会导致抖动测量不准确。有时标准会暗示要在测试中使用时钟恢复,例如提到“黄金PLL”,或指定要“在使用以20dB/decade将抖动衰减到(比特率/1,667)频率以下的单极、高通、频率加权函数后”测量抖动。

扩频时钟(SSC) 把时钟能量(和数据)扩散在0.5%的频段上,降低了频谱给定频率上的平均功率。这可以帮助产品满足放射辐射和传导辐射的法规要求。为成功地追踪SSC,接收机必须能够追踪调制(包括其谐波),以避免眼图闭合。如果环路响应未能充分追踪SSC,或在时钟和数据路径之间出现错误的延迟,那么测试眼图就会模糊闭合。

不正确的峰值(即LBW附近区域,这里的时钟恢复设备抖动输出可能会大于抖动输入)可能会放大被测的抖动数量。此外,测试设备中相对于输入数据信号的触发延迟可能会导致测得的抖动数量不正确。例如,测量系统中的固定延迟可能会导致测得额外的明显抖动。增加的抖动幅度取决于相对于延迟量的抖动频率。

在接收机端,时钟恢复可能会出现在被测器件中,也可能作为测试设备校准程序的一部分出现。在被测器件中,时钟恢复频频出现,在测试中通常使用压力和正弦曲线抖动实现(参见图1中的b部分)。在正弦曲线抖动中,测试一般使用模板,这会在较低的调制频率上应用较多的抖动,或在较高频率上应用较少的抖动。

其中的问题包括在接收机中使用设计不当的LBW,这会导致抖动容限模板失效。追踪响应的斜率不正确可能会使追踪SSC的准确性不够,导致测试眼图模糊闭合,并产发生误码。

时钟恢复被频繁用于测试设备设置及接收机抖动容限或受压的眼图信号校准(参见图1中的c部分)。正弦曲线抖动通常设置成频率高于校准过程中时钟恢复的LBW。但是,LBW不正确可能会导致压力量设置错误,进而造成被测器件压力不足或过大,前者会提高客户拒收的可能性,后者则会影响良率。

从所有这些情况中,很容易得出这样的结论,即LBW设置非常关键,对测量中观察到的抖动有着明显影响。改变环路带宽可以显示抖动频谱。以非常窄的LBW进行测试,可以显示被测发射机产生的所有抖动。而使用非常宽的LBW进行测试,则只会显示发射机产生的、预定系统接收机用自己的PLL不能滤掉的抖动。一般来说,一致性测试中会指定后一种时钟恢复方式。系统设计人员主要关心超出接收机追踪能力的抖动。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网