我们的设计需要多大容量的芯片?我们的设计能跑多快?这是经常困扰工程师的两个问题。对于前一个问题,我们可能还能先以一个比较大的芯片实现原型,待原型完成再选用大小合适的芯片实现。对于后者,我们需要一个比较精确的预估,我们的设计能跑50M,100M 还是133M?

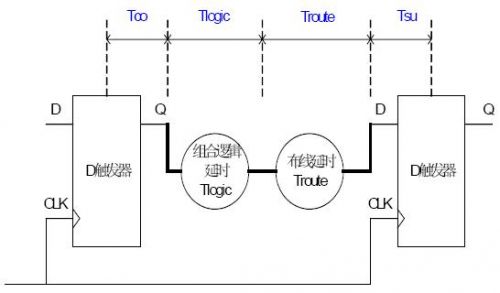

首先让我们先来看看Fmax 是如何计算出来的。图(1)是一个通用的模型用来计算FPGA的。我们可以看出,Fmax 受Tsu , Tco , Tlogic 和 Troute 四个参数影响。( 由于使用FPGA 全局时钟,时钟的抖动在这里不考虑)。

时钟周期 T = Tco + Tlogic + Troute + Tsu

时钟频率 Fmax = 1/Tmax

其中:

Tco : D 触发器的输出延时

Tlogic : 组合逻辑延时

Troute : 布线延时

Tsu : D 触发器的建立时间

图( 1 ) 时钟周期的计算模型

由图(1)可以看出,在影响Fmax 的四个参数中,由于针对某一个器件Tsu 和Tco 是固定的,因此我们在设计中需要考虑的参数只有两个Tlogic 和Troute.通过良好的设计以及一些如Pipeline 的技巧,我们可以把Tlogic 和Troute 控制在一定的范围内。达到我们所要求的Fmax.

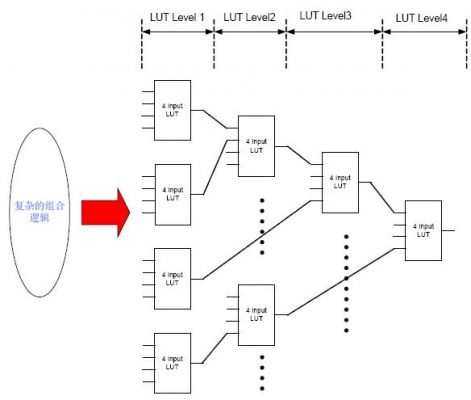

经验表明一个良好的设计,通常可以将组合逻辑的层次控制在4 层以内,即( Lut Levels 《=4 ) 。而Lut Levels( 组合逻辑的层次 )将直接影响Tlogic 和Troute 的大小。 组合逻辑的层次多,则Tlogic 和Troute 的延时就大,反之, 组合逻辑的层次少,则Tlogic 和Troute 的延时就小。

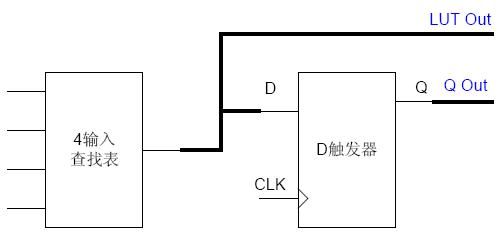

让我们回过头来看看Xilinx 和Altera 的FPGA 是如何构成的。是由Logic Cell ( Xilinx )或 Logic Element( Altera )这一种基本结构和连接各个Logic Cell 或Logic Element 的连线资源构成。无论是Logic Cell 还是 Logic Element ,排除其各自的特点,取其共性为一个4 输入的查找表和一个D 触发器。如图(2)所示。而任何复杂的逻辑都是由此基本单元复合而成。图(3)。上一个D 触发器的输出到下一个D 触发器的输入所经过的LUT 的个数就是组合逻辑的层次( Lut Levels )。因此,电路中用于实现组合逻辑的延时就是所有Tlut 的总和。在这里取Lut Levels = 4 。故Tlogic = 4 * Tlut 。

图( 2 ) FPGA基本逻辑单元

图( 3 ) 复杂组合逻辑的实现

解决的 Tlogic 以后,我们来看看Troute 如何来计算。由于Xilinx 和Altera 在走线资源的设计上并不一样,并且Xilinx 没有给出布线延时的模型,因此更难于分析,不过好在业内对布线延时与逻辑延时的统计分析表明,逻辑延时与布线延时的比值约为1:1 到1:2.由于我们所选用的芯片大量的已经进入0.18um 和0.13um 深亚微米的工艺,因此我们取逻辑延时与布线延时的比值为1:2.

Troute = 2 * Tlogic

Tmax = Tco + Tlogic + Troute + Tsu

= Tco + Tsu + 3 * Tlogic

= Tco + Tsu + 12 * Tlut

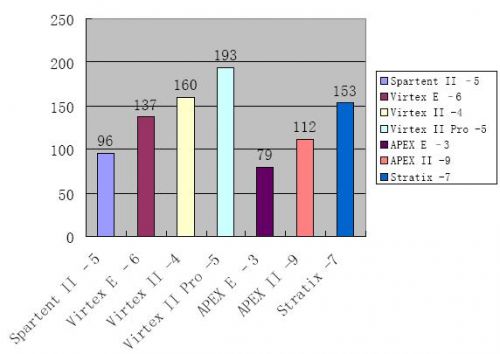

下表是我们常用的一些 Xilinx 和Altera 器件的性能估算。我们选取的是各个系列中的最低的速度等级。由于Altera 的APEX ,APEX II 系列器件的不同规模的参数不同,我们选取EP20K400E 和 EP2A15 作代表。

| Tsu ( ns ) | Tco ( ns ) | Tlut ( ns ) | Fmax | |

| Spartent II-5 | 0.7 | 1.3 | 0.7 | 96 M |

| Virtex E-6 | 0.63 | 1.0 | 0.47 | 137M |

| Virtex II-4 | 0.37 | 0.57 | 0.44 | 160M |

| Virtex II Pro -5 | 0.29 | 0.40 | 0.37 | 193M |

| APEX E-3 # | 0.23 | 0.32 | 1.01 | 79M |

| APEX II-9## | 0.33 | 0.23 | 0.7 | 112M |

| Stratix -7 | 0.011 | 0.202 | 0.527 | 153M |

# 以EP20K400E-3 的数据计算得出。

## 以 EP2A15-9 的数据计算得出。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网