摘要:数字化语音存储与回放系统的作用是对语音进行录音和放音,并实现数字化控制。能够做到语音回放的方法有很多,本课题研究的是基于FPGA控制下的语音存储与回放系统。

关键词:语音录放;数模转换;模数转换;FPGA

1 设计要求

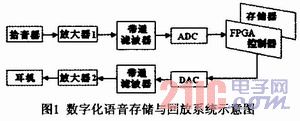

设计并制作一个数字化语音存储与回放系统,其示意图如图1所示。

(1)放大器1的增益为46dB,放大器2的增益为40dB,增益均可调;

(2)带通滤波器:通带为300Hz~3.4kHz;

(3)ADC:采样频率fs=8kHz,字长=8位;

(4)语音存储时间≥10s;

(5)DAC:变换频率fc=8kHz,字长=8位;

(6)回放语音质量良好。

不能使用单片语音专用芯片实现本系统。

2 数字化语音存储与回放系统硬件电路

2.1 放大器1即音频信号放大电路

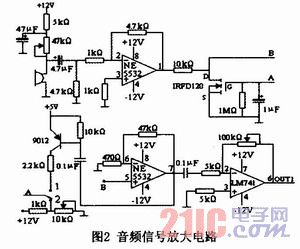

音频信号放大电路如图2所示。第一级放大(-4.7)倍。IRD120实现自动增益控制,当开关打到1的位置是增益自动控制,当开关打到2的位置是手动控制。增益自动、手动控制是利用场效应管工作在可变电阻区,漏源电阻受栅源电压控制的特性。第二级放大(+101)倍。第三级放大倍数可调,最大(-20)倍,保证ADC0809满量程转换。

2.2 带通滤波器

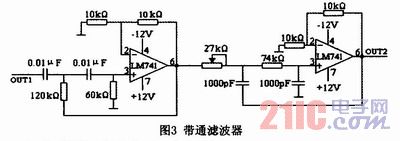

带通滤波器如图3所示。实测带通300~3300Hz。保证语音信号不失真地通过滤波器,滤除带外的低频信号和高次谐波。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网