FIFO是一种常用于数据缓存的电路器件,可应用于包括高速数据采集、多处理器接口和通信中的高速缓冲等各种领域。然而在某些应用,例如在某数据采集和处理系统中,需要通过同步FIFO来连接8位A/D和16位数据总线的MCU,但是由于目前同步FIFO器件的输入与输出数据总线宽度相等,不能满足这种应用,因此通常采用输入与输出数据总线宽度均为8位的同步FIFO作为它们之间的数据缓冲,并对MCU数据总线的高8位采用软件进行屏蔽,或是在同步FIFO外围增加数据锁存器及逻辑控制器件的方法解决。为了提高效率和降低系统设计的难度,本文采用VHDL描述语言,充分利用Xilinx公司Spartan II FPGA的系统资源,设计实现了一种非对称同步FIFO(输入与输出数据总线宽度不一致的同步FIFO),它不仅提供数据缓冲,而且能进行数据总线宽度的转换。

非对称同步FIFO的设计难点

对于非对称同步FIFO的设计来说,不能简单地通过修改现成的同步FIFO模块而得到,这是因为非对称同步FIFO的设计有以下几个需要解决的难点问题:

(1) 写数据与读数据总线宽度不同。设写数据与读数据总线宽度分别为Win和Wout,必须对Win>Wout和Win<Wout这两种情况进行写数据与读数据总线宽度的正确转换。

(2) 如何协调内部处理过程中不同的时钟频率。例如输入2个8位字节需2个时钟周期,而输出1个16位字节只需1个时钟周期,所以必须为内部数据处理提供不同的时钟频率。

(3) 由于写数据与读数据总线宽度不同,所以,要操作正确,必须保证数据存储排列的顺序及空/满标志产生的正确。

另外,由于FPGA中的寄存器个数有限,而FIFO是一种基于RAM的器件,需要占用大量的存储空间。通常在编写VHDL程序时用数组描述的方法来设计数据存储结构,在综合时会耗用大量的寄存器,所以这种方法在FIFO的设计中是不可行的。

非对称同步FIFO的设计

针对以上设计中的难点,本文采用VHDL描述语言,利用Xilinx公司Spartan II FPGA设计实现了一种非对称同步FIFO,设计中充分利用了FPGA中的资源如时钟延迟锁相环(DLL)和BlockRAM。

FPGA中的DLL

FPGA 中的DLL是一种很好的资源,Xilinx公司Spartan II、Spartan IIE、Virtex-E等系列器件中就采用时钟延迟锁相环技术进行FPGA内部的时钟控制,它可以对时钟进行倍频、锁相等操作。

本设计中要利用Spartan II系列器件中的DLL产生二倍频时钟信号。其中IBUFG、IBUF、BUFG、OBUF是时钟缓冲器,提供时钟信号的最小时延。

FPGA中的RAM

Xilinx公司的FPGA器件提供了片内RAM可供直接使用,而不必使用寄存器来构成存储空间,从而大大提高了芯片的利用率。根据型号的不同,FPGA中提供了两种结构的RAM:分布式RAM和BlockRAM。分布式RAM可以利用可配置逻辑模块(CLB) 设计实现,主要用于小容量片内存储;BlockRAM是FPGA内部的专用RAM模块,通常沿芯片的垂直边排列。根据具体型号不同,FPGA内部的BlockRAM在单位容量和总体容量上都有较大的不同。本设计将采用BlockRAM用于FIFO的编写。由于在Xilinx公司Spartan II FPGA器件库中没有现成的宏模块,就需要自己生成BlockRAM模块,具有较高的灵活度。利用Xilinx公司的配套软件ISE Foundation和ISE WebPACK中都带有的CoreGenerator程序包,可以很方便地建立用户所需的模块。只需要输入BlockRAM模块的名称、BlockRAM的类型(如单口还是双口)、地址线和数据线的宽度,就可以生成用户希望得到的结构。一般来说,生成的结构会自动加载到当前的项目中,从而可以像器件库中的元件一样调用。

非对称同步FIFO的结构

下面以Win<Wout(设Win=8,Wout=16)这种情形为例,介绍非对称同步FIFO模块的设计。非对称同步FIFO的结构框图,图中还显示了各模块端口及信号互连关系。其主要设计特点为:

(1) 由于写数据与读数据总线宽度不同,所以在设计双口RAM时把双口RAM设计成写口RAM和读口RAM两个部分。例如FIFO写口RAM部分为512×8,读口RAM部分为256×16,这样通过数据存储格式的改变达到写数据与读数据总线宽度的转换。

(2) 由于读数据时钟频率是写数据时钟频率的两倍,因此可利用FPGA中的DLL产生二倍频时钟信号来提高写数据的时钟频率,使读数据和写数据的时钟频率相等。二倍频时钟信号提供给写口RAM、写地址产生模块,而源时钟信号(一倍频)提供给读口RAM、读地址产生模块及空/满标志产生模块,从而解决了内部数据处理同步的问题。

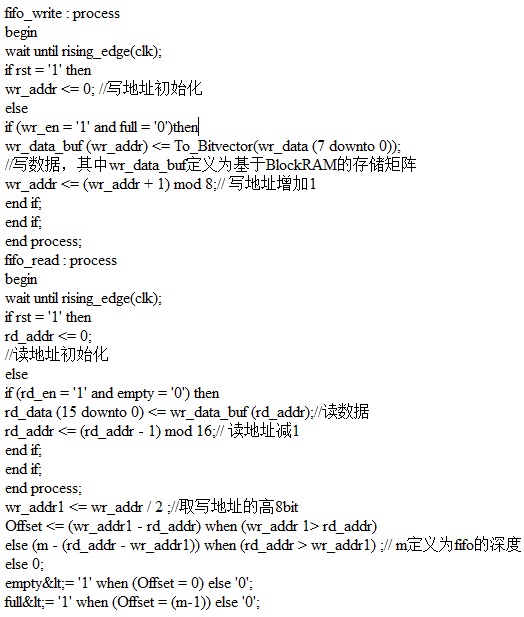

(3) 由于双口RAM中存在两种数据存储格式,因此地址位数不同,读地址和写地址不能一一对应,例如FIFO写口RAM部分为512×8,读口RAM部分为256×16,因此写地址要求9位,而读地址要求8位,对于同一数据的写地址与读地址,写地址的高8位与读地址的8位相等,它们的区别仅在写地址的最低一位。因此可把写地址的高8位与读地址一同输入空/满标志产生模块,从而得到正确的full和empty信号。下面仅给出读写地址产生逻辑及空/满标志产生逻辑的VHDL设计程序:

方案实现

文中用VHDL语言描述了硬件结构,在Xilinx 公司Spartan II FPGA XC2S100-TQ144中通过了Xilinx ISE WebPACK的综合及布局布线。FPGA的规模是10万门,速度可达到56.344MHz。

有几点需要说明的是:(1) VHDL程序设计采用多层次的结构设计方法,把系统分解成若干个模块,其中模块又由若干个元件构成。设计从元件开始,其中设计中用到的CLKDLL、IBUFG、IBUF、BUFG、OBUF等元件位于Xilinx公司 FPGA专用器件库UNISIM中,在编写VHDL程序时,用COMPONENT和PORT MAP指令调用专门的模块,就可以在程序中导入所需元件。(2) 作为非对称同步FIFO,用波形图的方式进行仿真不太合适,可用VHDL建立测试平台的方式进行仿真,测试平台中把非对称同步FIFO主程序作为一个元件调用,主要包括初始化、时钟产生块、读写数据等内容,输入激励由测试平台产生。(3)由于Spartan II FPGA中BlockRAM单位容量和总体容量有限,如XC2S100中BlockRAM的单位容量为4Kbit,共10个, 则总体容量为40Kbit。设计时可以用多个BlockRAM组成不同深度和宽度的存储单元,如果容量还是不够则需要选用其它型号的FPGA。

结语

采用本文的设计思路,同样可以设计出Win>Wout情形下的非对称同步FIFO,而且该方案具有很强的灵活性并易于实现。如通信只需单向进行,则只用一片FPGA即可;双向通信时需用两片FPGA。经过实际验证,该方案可以满足一般需要.

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网