随着CCD(电荷耦合器件)和CMOS(互补金属氧化物半导体)图像传感器制造工艺的发展,图像传感器的分辨率越来越高,如果要实时显示图像传感器采集到的图像,则要求图像处理芯片有较高的运行速度,但由于需要处理的数据量太大,一般的数字信号处理器很难直接输出分辨率为1024×768,帧频为60 Hz的标准XGA信号。这就需要对DSP输出的图像数据进行处理,使图像能够在VGA显示器上实时显示。市场上虽然也有一些专门图像处理芯片,但其价格昂贵,且应用于特殊场合。本文设计的显示控制器可以达到提升帧频的功能,可使输入分辨率为1024×768,帧频为7.5HZ的YCbCr(4:2:2)图像信号提升到帧频为60HZ,并通过色空间转换,将YCbCr(4:2:2)图像信号转换成RGB格式的标准XGA信号,同时产生符合VESA标准的XGA格式的行、场同步信号,输出信号经D/A转换后可直接输出到VGA接口,从而可使图像传感器采集到的图像数据能够在VGA显示器上实时显示。

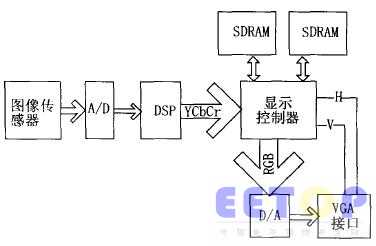

随着微电子技术及其制造工艺的发展,可编程逻辑器件的逻辑门密度越来越高,功能也越来越强,由于FPGA器件的可并行处理能力及其可重复在系统编程的灵活性,其应用越来越广泛。随着微处理器、专用逻辑器件、以及DSP算法以IP核的形式嵌入到FPGA中,FPGA可实现的功能越来越强,FPGA在现代电子系统设计中正发挥着越来越重要的作用。本文设计的显示控制器就是用VHDL语言描述,基于FPGA而实现的。该系统硬件框图如图1所示。

图1 系统硬件框图

1 显示控制器的设计

1.1 工作原理

图像传感器采集到的原始图像数据,经过A/D转换及DSP处理后,生成每秒7.5帧的图像数据,该数据是分辨率为1024×768的YCbCr(4:2:2)格式的16位图像数据。DSP输出到FPGA的信号有象素时钟,行、场参考,图像数据。FPGA在输入的行、场参考都有效时,在输入象素时钟的同步下,接收图像数据,并送入到SDRAM中, 同时从另一个SDRAM 中读取数据,并通过色空间转换,将YCbCr(4:2:2)信号转换成RGB信号。当SDRAM 中写满一帧图像数据时,控制器对两个SDRAM进行读、写切换。由于写数据速率小于读数据速率,所以在往一个SDRAM写满一帧图像数据的时间内,控制器能够连续多次从另一个SDRAM中读出另一帧图像数据,从而实现了提高帧频的目的。FPGA输出的RGB格式数据经D/A转换后,将数据转换成模拟信号,配合行、场同步信号可使其在VGA显示器上显示。外部晶振输入32.5MHZ的时钟,该时钟在FPGA内经时钟锁相环倍频后产生65MHZ的主时钟,用于对两个SDRAM进行读写和用来产生符合VESA标准的XGA格式的行、场同步信号。

1.2 控制器的内部模块介绍

本设计采用模块化设计原则,按照现代EDA工程常用的“自顶向下“的设计思想,进行功能分离并按层次设计,用VHDL语言实现每个模块的功能。该显示控制器主要由以下七个功能模块组成:

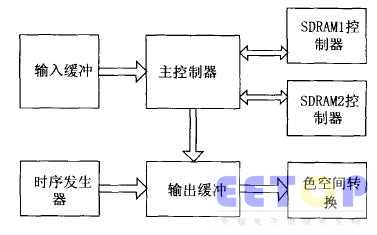

该显示控制器的内部结构如图2所示。上电后,显示控制器首先对两片SDRAM进行初始化,初始化结束后,其它模块才开始工作。下面将详细介绍各个模块的功能及设计思想。

图2 显示控制器的内部结构

1.2.1 数据输入缓冲模块

数据输入缓冲模块为深度为1024、宽度为16bit的异步FIFO (先进先出),写时钟为DSP输出的12MHZ的象素时钟,读时钟为经时钟锁相环倍频后的65MHZ的主时钟,通过场下降沿检测,来确保从一帧开始时接收数据。当输入的原始图像数据的行、场参考信号都有效时,该FIFO的写使能有效,在输入象素时钟的同步下,开始接收数据,写地址计数器为0到1023的循环计数器,当其计数到511或1023时,给主控制器发读信号,主控制器随后产生FIFO的读使能信号,使读使能信号在连续的512个读时钟周期内一直有效,即可连续读出512个数据。由于读时钟频率大于写时钟频率,所以不会产生数据写满溢出的现象。

1.2.2 主控制器模块

该模块为显示控制器的主要控制部分,通过对输入缓冲的读请求信号和输出缓冲的写请求信号处理,来实现对两个SDRAM的读、写切换。上电后,该模块接收从输入缓冲中读出的数据并将其写入到SDRAM 1中,同时从SDRAM2中读出数据,送入到输出缓冲中,当然最初读出的数据为无效数据。当SDRAM1中写满一帧图像数据,即1024×768个有效数据后,该模块对两个SDRAM进行读、写切换,即将接收数据写入到SDRAM2中,同时从SDRAM 1中读出数据,一直按此规则进行读、写切换。两个SDRAM的读、写地址发生器靠主控制器内部的计数器来实现。

1.2.3 SDRAM控制器模块

该模块首先完成对SDRAM 的初始化,初始化过程为:上电后等待200 us,然后对所有BANK发预充命令,接着发出八个自动刷新命令,然后进行模式设置,模式设置时将SDRAM设置成连续的全页并发模式,即512并发。

初始化结束后,SDRAM进入正常工作状态,准备接收读、写命令。当SDRAM在空闲状态下,为保持其数据不丢失,必须对其进行定时刷新,一般要求64ms内刷新4096次,通常根据时钟频率,用计数器计时钟脉冲到15.625 us时,发自动刷新命令,但是当SDRAM在进行读、写进发时,自动刷新命令会打断读、写,从而造成数据丢失。该设计中,由于在64ms内对SDRAM至少进行4096次读、写操作,所以可以不必对其进行刷新。

由于SDRAM被设置成全页并发,预充命令可停止并发,所以当SDRAM读、写到511时,发出预充命令,来停止并发,同时关闭当前行,为下一次读、写作好准备。SDRAM初始化后,其状态转移图如图3所示。

图3 SDRAM初始化后的状态转移图

1.2.4 时序发生器模块

该模块为输出行、场同步产生模块,利用FPGA内部时钟锁相环倍频后的65MHZ的主时钟产生符合VESA标准的分辨率为1024×768、帧频为60HZ的标准XGA格式的行、场同步信号,同时在行、场参考信号都有效时产生一个信号给输出缓冲模块,作为输出缓冲的读使能信号。根据VESA标准,分辨率为1024×768、帧频为60HZ的标准XGA信号的象素时钟为65MHZ,行同步信号的有效时间相当于1024个象素时钟周期,同步头宽度相当于136个象素时钟周期,前肩宽度为相当于26个象素时钟周期,后肩宽度为相当于162个象素时钟周期。场同步信号的有效时间相当于768个行周期长度,同步头为6个行周期长度,前肩为3个行周期长度,后肩为29个行周期长度。根据此标准,当行、场参考信号都有效时,一幅图像可输出1024×768个有效数据。该模块的时序仿真波形如图4所示。

1.2.5 输出缓冲模块

该模块为深度为1024、宽度为16bit的异步FIFO(先进先出),写时钟和读时钟同为65MHZ的主时钟,SDRAM初始化结束后,该模块先从SDRAM2中读出1024个数据,然后才使时序发生器模块开始工作,当读使能有效时,在读时钟同步下,读地址计数器从0到1023循环计数,当计数器计到100或700时,该模块向主控制器模块发写请求命令,从而每次可从SDRAM中连续读出512个数据,由于在输出行、场消隐期间,读使能信号无效,所以,不会产生读空现象。

1.2.6 色空间转换模块

输出缓冲模块输出YCbCr(4:2:2)格式的信号,其输出顺序如表1所示。本设计采用临近插值法,插值后的YCbCr格式如表2所示。

| Y0Cb0 | Y1Cr0 | Y2Cb2 | Y3Cr2 | Y4Cb4 | Y5Cr4 | …… |

| Y0Cb0Cr0 | Y1Cb2Cr0 | Y2Cb2Cr2 | Y3Cb4Cr2 | Y4Cb4Cr2 | …… |

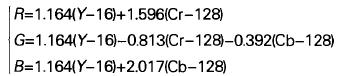

YCbCr色空间到RGB色空间的转换公式为:

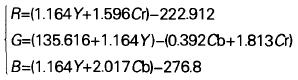

其中Y的范围是(16,235),Cb、Cr的范围是(16,240),为了防止相减后为负出现溢出,对转换公式变形得:

用VHDL语言描述小数乘法时,通常是将小数扩大2的整数幂次方倍后,取整进行乘法运算,然后将结果进行移位操作。当需要对运算结果进行四舍五入时,可以在运算时加0.5,然后对运算结果取整。下面将对R的运算过程进行描述,运算精度取11位。

R=(1.164Y+1.596Cr)-222.912+0.5

= (1.164Y+1.596Cr)-222.412

= (1/211) [(2384Y+3296Cr)-455499]

将方括号中的运算结果右移11位,即可得到R的值。Cb、Cr的运算过程与此类似。

色空间转换模块输出24bit RGB(8:8:8)信号,该信号经D/A转换后,配合时序发生器模块产生的行、场同步信号,即可在VGA显示器上显示。

色空间转换模块之所以放在输出缓冲模块后,主要是为了减少输入缓冲和输出缓冲模块中的先进先出及SDRAM的存储空间,如在相同精度下,SDRAM存储一帧图像将会占用1024×768×24bit的存储空间,色空间转换模块放在输出缓冲模块后,将会减少1/3的存储空间。

2 显示控制器的硬件实现

该显示控制器是基于Xilinx公司的Spartan-IIE系列FPGA XC2S300E-6-PQ208C设计实现的。此FPGA逻辑资源丰富,其内有30万个系统门,6912个逻辑单元(LC),1536个可配置逻辑快(CLB),64Kbit的块RAM,146个可用的I/O口,4个数字延迟锁相环(DLL)。块RAM可实现大量数据的内部存储,延迟锁相环可对时钟进行管理,可自动调整并消除输入时钟与FPGA内部时钟之间的相位偏移,同时还可实现对时钟的分频、倍频和移相。

用于帧缓存的两个SDRAM 的型号为HY57V281620HCST,此SDRAM 为Hynix公司生产的高速存储器,其内有四个Bank,每个Bank的存储空间为2M×16bit,可应用于需存储大量数据的场合。

3 结论与展望

本文设计的显示控制器具有很强的灵活性,当输入图像格式改变时,只需在色空间转换模块做相应修改,便可实现不同格式图像的VGA显示。基于该显示控制器而研发的高分辨率监控摄像机、数字视频展台等产品可广泛应用在教育、银行、煤矿、交通、医疗等领域。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网