0 引言

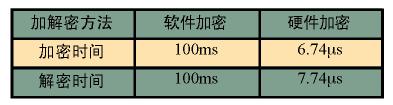

利用软件实施加密算法已经成为实时安全通信系统的重要瓶颈。标准的商品化CPU和DSP无法跟上数据加密算法的计算速度要求。此外,CPU和DSP需要完成太多的其他任务。基于FPGA高度优化的可编程的硬件安全性解决方案提供了并行处理能力,并且可以达到所要求的加密处理性能基准[1].然而如果仅使用FPGA可编程VHDL来实现的话,系统就不够灵活,升级困难,况且实现起来有很大的难度,本系统以AES加密算法为例,使用Xilinx SPARTAN 3E为开发平台,以Xilinx的嵌入式软核Microblaze为主控制器,调用FPGA的硬件VHDL编程实现的AES加解密和控制CC2420来实现高速有效的数据通信。

1 系统设计思想

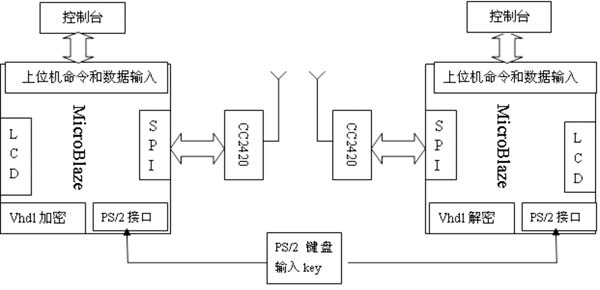

本设计使用硬件描述语言VHDL在FPGA数字逻辑层面上实现AES加解密,为了系统的扩展性和构建良好的人机交互,设计通过PS/2键盘输入加密密钥,并将其显示在LCD上。在软核MicroBlaze上,通过SPI总线读写FIFO和RAM控制射频芯片CC2420,使系统具有信道选择、地址识别、自动CRC校验功能,使系统更加安全、通信误码率更低。

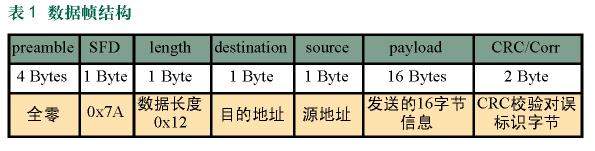

1.1 数据帧结构设计

为了更好的提高本系统数据的传输率,在官方zigbee的数据帧格式基础上做了修改。采用如表5-2所示的数据帧格式。数据帧发送时,CC2420自动在数据包的开始处加上前导码和帧起始分隔符在数据包末尾加CRC检验。

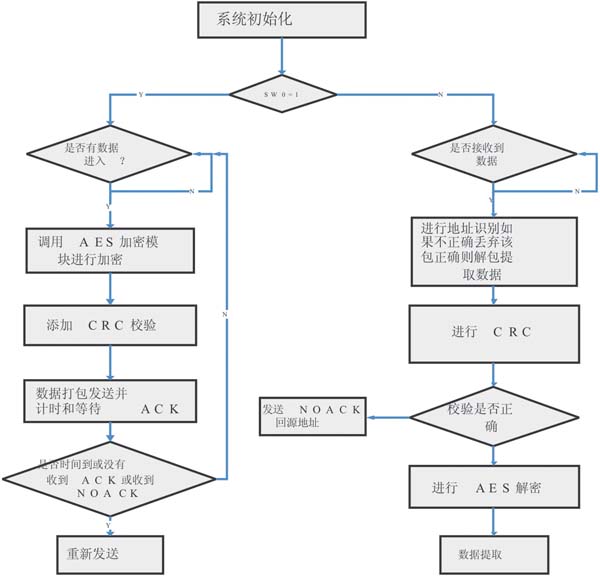

1.2 数据可靠传输

为了确保数据不出错和不丢失,本设计采用了CRC校验、超时重传、返回ACK和NOACK等措施来确保数据的不出错和丢失,

2 系统模块构成

加密端通过串口和网口从发送段接收数据,当接收够16字节(128bit),或不足时能自动补零成128bit后送给硬件AES加密模块。在软核Microblaze的控制下通过VHDL编程的AES加密后将数据进行组帧打包,通过软核对CC2420的寄存器的读写将数据通过无线发送端CC2420发送出去,同时等待发送段确认。接收端在接收到数据以后,从数据包中将数据提取,进行快速AES解密,解密完成后进行CRC校验,如果校验正确则向源地址发送ACK确认。将正确数据送出,如果校验失败,则返回NOACK。为了确保安全,AES加解密算法需要的密钥key由键盘输入和修改,同时可以在LCD上显示出来。必须保证两端key相同才能保证正常通信。

3 AES加解密模块

3.1.1 AES简介

AES加解密算法(Rijndael算法)对待加密的明文先进行分段然后加密,明文的长度可以是l28位、192位或256位。同样,用于加密的密钥长度也有l28位、192位或256位。根据明文及密钥长度不同的组合,加密的轮次有10轮、12轮和l4轮。在圈函数的每一圈迭代中,包括4步变换,分别是字节代换运算、行变换、列混合以及圈密钥的加法变换。经过验证,选用l28位的明文和密钥是几种组合中加解密速度最快的[2]。所以在本系统设计中使用的为128位明文和128位密文的组合。由于AES为对称加解密,所以在此文中我们只讨论AES的加密方法,解密就是与AES对称的方式来进行的。

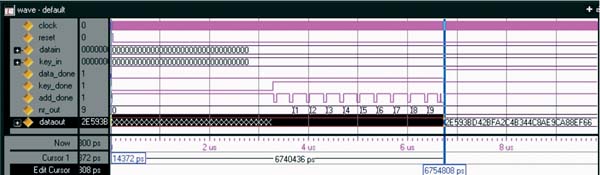

3.1.2 AES加解密模块设计

在本系统中,使用了FPGA的硬件描述语言(VHDL)来实现了AES的加解密算法,AES分别为轮密钥加、字节代换、行移位、列混淆、密钥扩展,下面为5个用硬件描述语言实现的小模块的分别介绍。由于列混淆模块、行移位模块、轮密钥加与文献[4]中算法相同在此不做讨论。

① 字节代换模块

此模块为AES中的每一个字节提供了一个非线性代换。任一非零字节被函数所代替。如果x是零字节,y=b 就是SubBytes变化的结果。在本设计中,为了加快算法速度,将S盒预先写入RAM中,直接用地址来指示替代的字节,利用空间来换时间,达到了加快用算的目的。

②密钥扩展模块

本设计采用了Xilinx IP核Single Block RAM 位宽32,深度64,在程序的开始,由用户设置的初始密钥系统按照密钥扩展算法生成的10轮扩展密钥,将生成的密钥按照地址次序从低到高放入RAM中,在每一轮执行addroundkey时取出对应轮数的密钥,与明文相加(异或)。

3.2 无线通信模块

在本系统中采用TI 公司的CC2420来实现数据的无线通信CC2420工作于免授权的2.4GHz频段,33个16位配置寄存器、15个命令选通寄存器、1个128字节的RX RAM、1个128字节的TX RAM、1个112字节的安全信息存储器。TX和RX RAM的存取可通过地址或者用两个8位的寄存器。主机可通过SPI总线设置其工作在Normal模式,通过SPI总线MOSI,MISO接口对TX FIFO和RX FIFO及状态进行写和读的操作,将数据写入和读出RAM来实现与CC2420的数据传输,通过触发CC2420STXON,SRXON来实现数据的无线发送和接收。表二是本系统CC2420涉及的寄存器及其功能。

表2 是本系统CC2420涉及的寄存器及其功能

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网