在技术发展的进程中,某些出现的里程碑式技术甚至引起了发展方

向的全盘改变。最初常用的并行打印机端口现在几乎已经绝迹了。系统结构以8/16/32位并行总线的方式实现硅器件和存储器之间的互连。传统的系统背板会

定义宽度达64位的并线总线。由于用户对更高保真度多媒体体验的需求不断提升,导致数据率不断提高,系统数据吞吐量的要求呈现几何级数的增长。不过,增加

并行总线的宽度和时钟的频率并不是长期可行的解决方案,因为这种方法本身已经达到了某些技术死角,主要会碰到的问题包括PCB的空间限制、信号噪声、信号

完整性和避免信号互相干扰、布线长度、建立和保持时间(setup & hold time) 的要求以及电磁辐射(EMI) 等。

如今,从板上器件之间到嵌入式系统和外部的接口,许多开发都采用高速互连,如RapidIO、XAUI、USB和HDMI等等。

高

速串行互连是标志并行数据总线向串行总线转变的技术里程碑,这种技术是减少设计师面临的信号阻塞问题的方法。这种转变是由业界对系统成本和系统扩展能力的

要求所推动的。随着芯片技术的发展和芯片尺寸的缩小,用速率达数千兆位的高速串行互连来取代传统的并行结构变得简单易行。

技术发展

低压差分信号技术(LVDS) 是隐含在许多高速串行互联标准定义后面的核心电子信号技术。当数据率高于3Gbps时,电流模式逻辑 (CML) 和低压正射极耦合逻辑(LVPECL) 是关键技术。

功耗和数据率是取舍各种信号技术方法的关键因素。

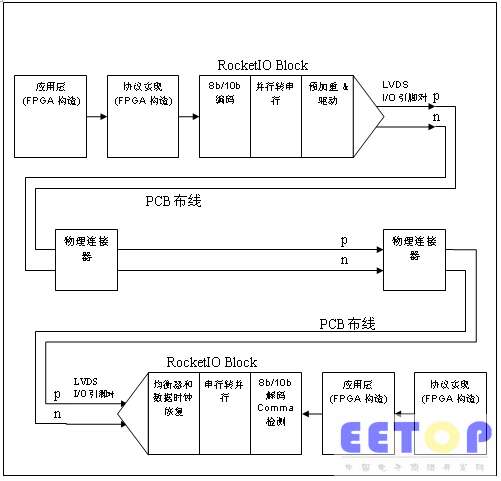

为进一步降低信令引脚的数量和信号布线的长度,从而降低电路板的设计复杂程度,时钟被嵌入到了数据中。在接收端,需要对时钟数据进行恢复,这种方法已经发展成熟并被许多串行通信系统所广泛采用。

此

外,为提高抗噪能力和共模抑制能力,LVDS信号技术大多采用交流耦合。这就需要直流平衡线路编码方案并保持有足够的切换用于时钟恢复。我们采用IBM开

发的8b/10b编码方案或类似的方案,将8位字转化成10位的符号并最终用于传输。8b/10b编码还包括用于同步的特殊控制字符(被称为“K字符”)

。

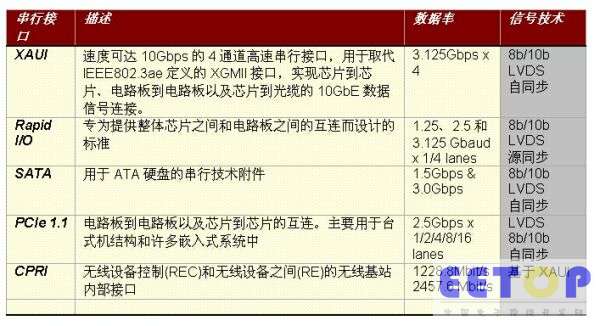

高速串行接口通常用于各种芯片之间的接口、背板的互连以及设备与设备的连接。以下是被广泛采用的一些串行互连协议:

芯片到芯片/背板串行互连:

- XAUI

- Rapid I/O

- SATA

- PCIe

- CPRI (控制设计和基站间的3G通信协议)

硬件机箱设备与设备的串行电缆接口:

- HDMI, DVI, 显示端口

- USB

- 1394

FPGA在数千兆位开发中的应用和设计挑战

高速串行协议开发的进展迅速,实现可靠设计解决方案成为设计师面对的挑战,因

此一种能方便进行设计变动、测试和调试的平台能有效帮助客户验证设计以及尽快将产品投放市场。Xilinx的Virtex系列FPGA

带有嵌入式RocketIO收发器硬内核,从而具备了这种灵活性。这种器件在一片器件中集成了最多24个RocketIO,能实现内部通道绑定的多通道方

式,也可以实现去失真。

利用Rocket

I/O内核在信号强度、信号预加重/去加重和数控阻抗方面的可编程性,很容易实现不同的I/O标准。利用FPGA来实现还可以在FPGA结构内部很快实现

标准协议。高速接口意味着器件内有大量需要处理的数据,而在FPGA内部很容易实现并行处理结构。我们相信,由于FPGA的成本已经开始下降且FPGA对

于不断发展的串行协议标准有更良好的适应性,将有越来越多应用采用FPGA而不是ASSP来进行接口标准的处理。

如同高速网络交换和采用多处理器结构的超级计算机一样,在多FPGA的设计中千兆位收发器的采用是必然的。带有RocketIO收发器的FPGA会成为连接处理器矩阵和FPGA的唯一互连选择,以确保整个板上处理器矩阵间的数据吞吐能力。

当实现高速串行连接时,不可避免地会碰到传输线的影响和信号完整性问题。这些都是高速互连设计中必须小心处理的难题。

时钟源&时钟抖动

串行数据抖动:

-总抖动

- 随机抖动

- 确定性抖动

- 信号调理特性

- 电缆和PCB布线中的介质损耗

- 预加重和去加重驱动器(频率选择性放大器和衰减器)

- 均衡(无源和有源均衡)

下面是一个通用数千兆位串行互连的实现框图及相关要求。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网