0 引言

脉宽调制技术(PWM)目前广泛应用在电力、电子、微型计算机、自动控制等多个学科领域。本设计采用基于FPGA的直接数字频率合成(DDS)技术,通过D/A转换进行程控放大,实现了三相功率可控的PWM信号。

1 系统的设计原理和实现过程

1.1 DDS的设计原理

直接数字频率合成器(DDS)的组成见图1。fc为时钟频率,K为频率控制字,N为相位累加器的字长,W波形存储器地址线位数,L为ROM数据线宽度(一般也为D/A转换器的位数),fo为输出频率。相位累加器按照时钟脉fc的时序,对输入频率控制字K进行累加,相位累加器的输出作为波形存储器的地址输入。相位累加器的输出对应于该时刻合成周期信号的相位,由于N位累加产生溢出,因而相位是周期性的,在0~2π范围内变化。2π/2N rad是最小的相位增量,完成一整周的正弦波输出需要经过2π/(K×2π/2N rad)个系统时钟周期。因此,可以得到输出波形的频率fo为:

而DDS的最小频率分辨率(即最低的合成频率)为

![]()

最高的基波合成频率受奈奎斯持抽样定理的限制(至少每周两次抽样才能重构波形)。

由此可以看出,DDS具有高频率分辨率的特点。在fc固定时,取决于相位累加器的位数N,只要N足够大,理论上就可以获得相应的分辨精度,这是传统方法难以实现的。DDS中相位改变是线性过程,其相位误差主要依赖于时钟的相位特性,相位误差小,形成的信号具有良好的频谱特性。

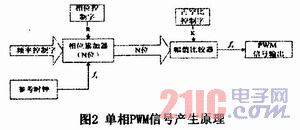

1.2 用FPGA和DDS技术产生三相PWM的原理

本设计需要设计能够输出三相的PWM信号。根据DDS的原理,相位累加器的输出对应于该时刻合成周期信号的相位,并且相位具有周期性,在0~2π范围内变化。因此设置相位累加器的初始值,就可以使产生的信号具有不同的初相位。

本设计的单相PWM信号在FPGA上实现的原理和过程如图2所示。相位控制字R设置相位累加器的初始值,可决定PWM信号的初相。图2中,使用一个幅值比较器取代了图1中的波形储存器,幅值比较器是一个0/1输出的二值比较器,它决定了输出脉冲的波形。由前面分析可知,累加器的输出值是线性的,它的值与相位一一对应,因此累加器的输出值与参数K进行比较结果决定输出信号fo的高低电平。K作为一个门限值,通过设置K便可设置输出脉冲波形的占空比,我们把K称为占空比控制字。多路单相PWM电路共用一个参考时钟fc就可以构成多相PWM信号,各相PWM均有独立的R和K,通过设置便可获得多路同频异相、占空比不同的PWM信号。

由于使用了DDS原理方法,上述PWM脉冲信号具有高频率和相位分辨率的特点。但图2中的DDS方法是有区别于传统DDS实现的,它没有使用波形存储单元,节省了FPGA的存储空间,使设计全数字化,便于在FPGA上实现,方法简单高效。

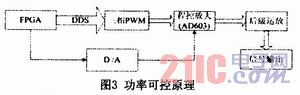

1.3 功率可控的设计

PWM信号的功率可控是为了满足不同应用的需求。本设计通过程控放大(AGC)实现PWM信号的功率可控,图3是功率可控的原理框图。

AD603是美国AD公司继AD600后推出的宽频带、低噪声、低畸变、高增益精度的压控VGA芯片。由FPGA、D/A转换器和可编程增益放大器AD603构成程控放大的原理如图3所示。FPGA通过对控制D/A输出直流电压来控制AD603的内部电阻衰减网络,实现增益调节。其外围元件少,电路简单,由于AD603带宽最大能达到90MHz,增益范围有40dB,增益精度在±0.5dB,可精确实现电压的控制,实现功率的精确步进控制。

2 设计的测试与结果分析

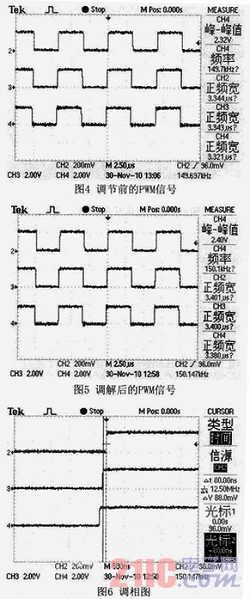

系统的测试结果如图4、图5及图6所示。

图1中的信号为作为比较的基准信号。信号的频率为149.7kHz,峰峰值2.32V,正频宽3.344μs,即占空比为50%。信号进行调幅、调频及调相后如图5所示,峰峰值为2.40V,步进增量为80mV;频率调为150.1 kHz,步进增量为0.4kHz;正频宽3.40 μs,占空比为51%;调相效果如图6所示,相位调节为2.16°。

测试设备为Tektronix TDS2024型的数字存储示波器。排除测试过程的误差,结果调制波形有较高的精度,基本达到了设计要求。

3 结论

基于FPGA实现的DDS的方法结合了FPGA及DDS的特点和优势,非常适用于产生频率、相位、占空比可调的信号,这恰好是PWM信号所需求的。目标系统实现了高精度、高分辨率的任意频率的三相PWM信号发生器的设计,在实测中取得了较好的效果。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网