引言

LCD因具有工作电压低、功耗小、显示信息量大、寿命长、易集成、方便携带和电磁辐射污染小等优点,在显示技术中异军突起,被广泛应用于手机、PDA产品、手持式仪器仪表等便携式电子产品与设备中。

LCD驱动电路是液晶显示系统的重要组成部分,是一种计算机(或MCU)和液晶屏之间的接口电路,其主要功能是通过调制输出到液晶显示器件电极上的电位信号的相位、峰值、频率等参数来建立交流驱动电场。由于LCD的规格相差较大,常规的方法是针对每一种LCD开发专门的驱动电路,这样的设计浪费时间,而且复用性较差。为此,设计一种可用于多数小规模LCD驱动电路的IP核,通过复用该IP核来解决这个问题是非常必要的。目前,国际上只有I-Shou大学的Yu-Jung Huang等人设计了可驱动不同规模LCD的驱动电路IP核,通过在系统中植入嵌入式微处理器来实现这一功能。但是,这种嵌入式微处理器使系统更复杂,而且成本更高。本文设计的可驱动不同规模LCD的驱动电路IP核是采用FPGA来实现的,能有效克服电路系统复杂和高成本这两个缺点。

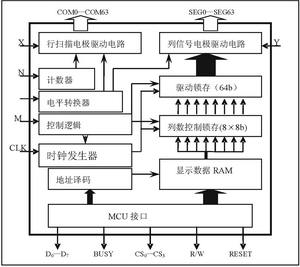

图1 IP核系统结构

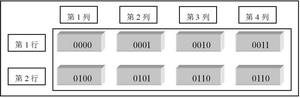

图2 IP核级联排列图(24)

设计规范

为了满足当今大多数较小规模的LCD显示应用的实际需要,本文所设计的LCD驱动电路IP核芯片具有64个COM(行)和64个SEG(列)输出,有高速的8位并行MCU接口及串行接口,芯片内含有存储显示数据的RAM,并专门设计了10个控制端,可以方便灵活地进行控制。它主要有以下几个主要功能:

1、为液晶显示屏提供扫描时序信号和显示信号数据;

2、支持以总线形式直接与MCU相连;

3、可驱动不同规模的LCD(n×m),n可以连续取值(n=0~63),m只可取8的倍数(m=8k,k取自然数);

4、支持IP核之间的级联以驱动较大规模的LCD,最大分别支持4个IP核行间级联和列间级联;

5、可以提供较宽的驱动输出电压范围以适应不同的LCD器件;

6、提供画中画、分屏显示等功能。

IP核的设计

本文按照“自顶向下”的设计方法,首先对芯片进行层次化功能划分,同时参照已有的LCD驱动芯片的设计经验, 并结合“自底向上”的设计方法对部分模块进行设计, 最后根据系统设计框架对各模块进行协调, 并进行芯片的整体功能验证, 从而达到了设计规范的要求。

系统结构

本文设计的IP核系统结构如图1所示。该IP核主要由下列几个模块组成:行扫描和列信号驱动模块、电平转换器、可预置数环形计数器、数据锁存模块、控制逻辑模块、显示数据RAM与地址译码模块、MCU接口模块。其中有的大模块还可细分为若干子模块。

各模块设计

MCU接口模块

MCU接口模块是IP核与外部控制器(MCU)通信的接口,是数据传输的通道。MCU通过该接口对LCD驱动芯片写入命令、读出状态或显示数据。同时该接口也接受命令译码器的控制,从而使读写与内部操作相结合。该芯片由较为复杂的内部组合逻辑和时序逻辑电路实现,可以兼容目前两种主流的MCU控制信号, 支持串/并行两种数据操作方式。

该模块内部除了包含现有常用LCD驱动电路的MCU接口模块中常用的几个子模块,如数据总线(8位)子模块、忙状态检测子模块、读写控制子模块、MCU释放子模块外,新加入了一个行级联和列级联控制子模块。数据总线主要用于内外部数据交换;忙状态检测子模块用于判断MCU状态,产生系统忙标志信号来协调信号的读写操作和接收内/外部复位信号;读写控制子模块用于产生正确的读写控制时序;MCU释放子模块的功能则为通过逻辑组合,在芯片执行“读-修改-写”过程时,释放MCU,以便MCU可以同时执行其它操作;而新加入的级联控制子模块的主要功能是实现IP 核之间的行级联和列级联,最多可支持16个IP级联(行列各4级),CS0~CS1是行级联控制端,CS2~CS3是列级联控制端。举例说明,假设有一种 LCD(128×256),可用8个IP核来驱动,设置时分别令CS为0000、0001、0010、0011、0100、0101、0110、 0111,就可以构成2×4的驱动IP核阵列,其排列示意图如图2所示。

显示数据RAM与地址译码模块

该模块主要用于存放将要显示的数据,在MCU接口和信号驱动电路之间起缓冲器的作用,以保证显示数据的稳定输出。

该模块包括存储显示数据的RAM阵列和地址译码器两个子模块。首先,由列地址电路提供列地址,通过列地址译码器选中一列8位的RAM存储单元,MCU通过接口对其进行读/写;然后,由行地址译码器对RAM以行为单位进行扫描,结合显示数据锁存电路可以实现整行数据的输出,通过电极驱动电路输出到液晶显示器以供显示。

数据锁存模块

该模块包含两个子模块:列数控制锁存子模块和驱动锁存子模块。列数控制锁存子模块由k个并联的8位数据锁存器构成,主要作用是锁存数据总线上的数据,在控制逻辑模块的控制信号和时钟信号作用下把从RAM上输出到8位数据总线上的显示数据信号分别锁存在相应的8位数据锁存器中,64位数据需要8次,每次8位输入。驱动锁存器子模块是一个由64个1位锁存器并联而成的64位驱动锁存器,它的作用是在控制逻辑模块的控制信号和时钟信号作用下把上面8个8位数据锁存器里传输来的m位数据一次全部锁存起来,然后输入到后面的列信号电极驱动模块。

控制逻辑模块

该模块的主要作用是控制信号数据传输和选择列信号线的数目。可以通过列数控制输入端M来控制列数控制锁存器子模块、驱动锁存器子模块和时钟发生器来实现适用于不同规模LCD的功能。根据需要,通过向列数控制输入端M输入不同的数值,来控制有多少位列数控制锁存器处于工作状态,其他的锁存器单元则置为空闲态。在工作周期内把显示数据RAM中的数据通过8位数据总线锁存到对应的列数控制锁存器中,然后在一个时钟信号控制下一次锁存到驱动锁存器中,以作为电极驱动模块的输入信号。这样,IP核可以实现控制选择驱动列数的功能。当M为“000”时,列数控制锁存器的低8位(第一个锁存器)工作,其它的全置闲,对应的列电极是SEG0~SEG7;当M为“001”时,列数控制锁存器的低16位(第一和第二个锁存器)工作,其它的全置闲,对应的列电极是 SEG0~SEG15;依次类推,直到列数控制锁存器64位寄存器全部工作,对应的列电极是SEG0~SEG63。

电极驱动模块

该模块主要含有四个子模块:行扫描电极驱动子模块、列信号电极驱动子模块、电平转换器和可预置数环形计数器。

电平转换器的作用是根据实际应用的需要,通过外加的控制信号将逻辑信号的电压转换为实际的LCD驱动电压,并输出到驱动模块;行扫描电极驱动子模块的作用是给行电极提供一定周期的扫描信号脉冲;列信号电极驱动子模块的作用是把来自锁存器的数据施加到相应的列电极,与行电极的扫描信号来建立交流驱动电场, 从而驱动LCD器件的显示。可预置数环形计数器可以通过行数控制端N(S0~S5)来控制行扫描电极数,以适应不同规模的LCD屏,根据实际的需要通过向行数控制端N输入不同的数值,来控制具体工作的行数,其它的电极全部置闲。在行驱动时钟信号控制下,逐行扫描,循环往复,直到行数控制端N输入新的数值, 再在新数目的行电极进行循环逐行扫描。例如,当外加信号N为“011011”时,扫描电极的数目为27,行扫描驱动子模块在行电极COM0~COM26上产生逐行扫描信号,其它行电极COM27~COM63全部都置为低电平,循环往复,若施加了新的外加信号N为“100011”,扫描电极驱动子模块就在行电极COM0~COM34上产生循环的逐行扫描信号。

IP核系统实现

首先,根据上面对整个系统功能定义和划分及对各个模块的设计,对各功能模块分别用VHDL语言进行建模;其次,在Xilinx公司的FPGA器件上,用其EDA工具 ISE进行仿真和综合调试,并优化设计;然后,用VHDL定义顶层模块将各模块连接起来,并进行相应的系统调试和验证;最后,得到一个LCD的驱动电路, 具有64个COM(行)和64个SEG(列) 输出,有高速的8位并行MCU接口及串行接口,芯片内含有存储显示数据的RAM,并且可以通过级联控制端CS来进行级联扩展以满足较大的LCD,通过列数控制端M和行数控制端N来适应不同规模的LCD。

仿真和验证

本文利用Xilinx公司的仿真软件ISE作为仿真工具,分两步对所设计的IP核进行了验证。

图3 行控制功能仿真结果

图4 列控制功能仿真结果

首先,本文先对IP核的各个模块(包括内部的子模块)进行了初步的功能验证。然后,参照芯片的工作过程,对整个芯片进行了整体仿真。图3和图4是利用 ISE对整个IP核的行和列控制功能进行仿真而得到的仿真结果。图中CLK和CLK1分别是MCU接口模块的数据传输控制时钟和行电极扫描脉冲;M和N分别为列电极与行电极数目选择控制端; CS的低两位和高两位分别为行级联与列级联控制端。

图3和图4的仿真结果说明:

1. 当RESET为高电平时,IP核处于初态或清零态;当WRITE为高电平时,IP核处于工作态,可以接收显示数据。

2. 在时钟CLK的上升沿,MCU通过接口向IP核的RAM并行写入8位显示数据;在时钟CLK1的上升沿,行扫描驱动电极依次输出扫描脉冲,列信号电极会把RAM里的数据从SEG上输出。

3. 行数控制端可以改变行扫描的电极数目。当行数选择控制端N为“3E”时,在COM0~COM61输出扫描信号。如图3所示,在第1个行时钟信号时,电极 COM61上输出扫描信号,在行驱动时钟控制下,逐行递减对行电极进行扫描;第7个行时钟信号时,N变为“22”,扫描信号变成在行电极COM33上输出,逐行递减对COM0~COM33进行逐行扫描。

4. 列数控制端可以改变列信号的电极数目。当列数选择控制端M为“110”时,SEG电极为48位输出;当M为“010”时,SEG的输出变为16位;当M为“101”,SEG的输出变为40位;当M为“100”,SEG的输出变为32位。

本文对该IP核的列数控制、行数控制、核间级联等功能分别进行了功能验证,并都通过了验证。此处限于篇幅只介绍了列数与行数控制功能。

结语

本文讨论了一种LCD显示驱动芯片IP核的设计,根据自顶向下的设计思想,将芯片进行了层次化功能划分,并对芯片的整体功能进行了验证。在芯片的功能验证中,本文采用了VHDL硬件描述语言对电路的逻辑功能和时序关系进行了仿真验证。该LCD显示驱动器由于采用了参数化设计,具有很好的移植性,可方便地应用于便携式仪器及PDA等有关产品的各种不同规模的平板显示系统应用中。

参考文献

1 .李维是、郭强,液晶显示应用技术,电子工业出版社,2000.3

2 .Yu-Jung Huang、Chih-Feng Liu,Design of LCD Driver IP for SOC Applications,IEEE Asia-Pacific Conference on Adcanced System Integrated Circuits(AP-ASIC2004),Aug.4-5 2004 ,pp.62-65

3 .Tien-Lung and Bergmann,Neil(2003)An interface Methodology fot Retargettable FPGA Peripheral,Proceeding of the International Conference on Engineering of Reconfigrable Systems and Alogorithms,June.23-26 2003,pp.167-173

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网