引言

随着应用的不断普及和深入,在设计嵌入式系统时,往往需要同时优化众多因素,如成本、功率、尺寸、性能、灵活性、产品上市时间、设计开发周期,以及可靠性等。Xilinx 公司推出的嵌入式处理器设计平台Virtex-II Pro和Virtex-4系列器件可以满足上述要求,其高性能的设计工具为设计者提供了完善的软硬件协同设计能力。本文以Virtex-II Pro P20 芯片内嵌PowerPC405硬核为处理器,选用目前广泛使用的VxWorks操作系统,阐述了内嵌PowerPC嵌入式设计的过程和要点,详细介绍了TCP/IP实时传输的整个设计过程,实验结果表明这种构架模式具有很好的应用前景。

基于FPGA片上PowerPC的嵌入式系统开发

随着嵌入式技术的发展,针对当前嵌入式处理器的应用,Xilinx公司推出了两款基于FPGA的32位嵌入式处理器内核。一种是采用先进IP植入技术实现的嵌入在Virtex-II Pro和Virtex-4器件中的PowerPC405处理器内核(这是业界目前唯一的嵌入式硬核),另一种是MicroBlaze 32位嵌入式处理器软核。硬核的好处是能够提供更快的数据处理能力,而软核则具有更好的灵活性,在目标器件中可以进行任意配置。由于硬核在速度和资源上具有优势,因此本文采用了PowerPC405处理器,它支持复杂嵌入式的应用模式。由于同时需要嵌入式RTOS VxWorks,而FPGA内部的BlockRAM往往不能满足提供较大存储空间的要求,因而一般要由外部的存储器阵列实现。

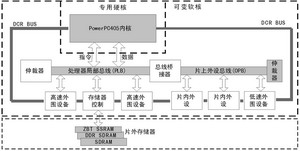

图1 PowerPC405复杂嵌入式应用模式

如图1所示,该体系结构主要应用于需要RTOS支持的数据处理、软件、控制等实时系统以及以FPGA为核心的复杂应用中。Virtex-II Pro系列器件采用IBM CoreConnect总线技术,该总线包括:处理器局部总线(PLB)、片上外设总线(OPB)和设备控制寄存器总线(DCR)。PLB总线为片内的高速数据通道,通常连接高速外设、DMA存储控制器等,OPB总线则通常用于连接速率较低的片上外设,二者通过总线桥接器与处理器总线连接,从而保证PLB 总线的高速特性。DCR总线用于实现PowerPC405的通用寄存器与逻辑设备控制寄存器的数据通信。

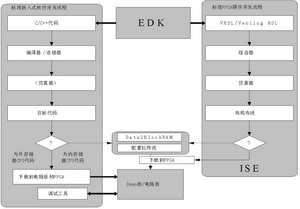

针对基于PowerPC405的平台FPGA设计,Xilinx公司推出了完整的软硬件协同设计工具EDK (Embedded Development Kit),它是一个专用于FPGA内部32位嵌入式处理器的集成化开发工具包,并提供硬件和软件协同设计的能力,从而极大地缩短了设计周期。在软硬件协同设计开发平台上,嵌入式软件工程师仍然可以独立地进行软件设计,硬件逻辑工程师也就可以继续采用过去的设计方法,如图2所示。

图2 嵌入PowerPC405的平台FPGA软硬件协同设计

在实际的软硬件协同开发时,如果不使用嵌入式RTOS,PowerPC405可以起到类似单片机的作用,软件开发就变得相对简单。而在一些大型项目的开发过程中,嵌入式RTOS往往是必需的,因此,研究嵌入式RTOS应用开发及其BSP的移植具有关键意义。

基于PowerPC405的VxWorks下的TCP/IP通信整体系统设计

VxWorks提供了丰富而标准的socket编程接口,可以方便地实现TCP/IP通信,同时,其多任务机制可以高效地完成实时任务的产生、调度、资源分配机制。本文在Virtex-II Pro开发平台上利用PowerPC405内嵌处理器和PC机进行TCP/IP通信,在底层使用100Mbps以太网作为传输媒介,实现了Vxworks嵌入式系统控制的文件实时传输。

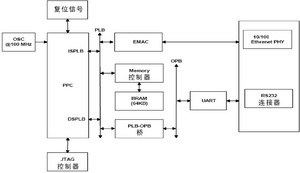

可以利用EDK中的BaseSystem BuilderWizard来快速构建基于PowerPC405的系统。首先设定参考时钟频率、处理器时钟、总线时钟,如果在设计中包含有100M网口,那么总线时钟必须选择100M以上的频率。然后选取相应的外设, RS232串口、100M以太网口、SDRAM等,其中plb_bram_if_cntrl外设是必选的,该控制器完成对BlockRAM的控制,保持CPU处于一个确定的状态。系统设计架构如图3所示,这里用到了EDK内带的Ethernet MAC LogiCore(图中的EMAC)。

图3 基于PowerPC405的TCP/IP通信整体设计框图

BSP开发和移植

嵌入式操作系统开发中一项非常重要的任务,就是BSP (板级支持包)的开发。这是一项非常复杂而繁琐的工作,Xilinx公司提供的EDK套件,可以在很大程度上减轻开发者的工作。EDK中的BSP生成器 (BSPgen)可以根据不同的微处理器、外设和RTOS组合自动产生用户可裁剪的BSP。它包含了系统所必需的支持软件,包括Boot代码、设备驱动和 RTOS的初始化。利用BSPgen可以把Xilinx器件驱动打包到BSP的子目录下,并且把Xilinx器件驱动与VxWorks及其Tornado 集成开发环境无缝集成,充分减少开发周期。

但是,BSPgen生成的BSP只是一个固定的BSP模板文件,不能自动设置RAM/ROM的存储器映射,不支持用户通过BSPgen流程自定义的核/驱动,不能自动集成总线错误检测,而且,Caches在缺省情况下被禁止的。

对于BSP开发人员来讲,借助EDK的BSPgen,还必须要做以下几项工作:

1) 准确定义RAM/ROM边界地址,修改configure.h和makefile文件(两者的地址定义必须相匹配);

2) 增加不能与VxWorks无缝集成的其他器件的驱动文件,如总线错误检测及报告、关键性中断、GPIO接口、I2C接口、SPI接口等;

3) 配置以太网参数,设置缺省的IP地址、MAC地址(sysNet.c文件中);

4) 配置内核服务选项,禁止/使能Cache和RAM,设置TCP/UDP/IP参数等;

5) 增加总线错误检测报告和关键中断支持文件。

经过以上修改之后,将BSPgen产生的BSP放在Tornado的安装目录…\target\config下,在Tornado集成环境下生成 Bootloader,然后就可以进行一般的嵌入式操作系统开发过程了。在这里,对BSP的修改只有config.h和makefile文件的 RAM/ROM地址定义,修改如下:

#define ROM_BASE_ADRS 0xff800000

#define ROM_TEXT_ADRS (ROM_BASE_ADRS)

#define ROM_WARM_ADRS (ROM_TEXT_ADRS+8)

#define ROM_SIZE 0x00400000

#define RAM_HIGH_ADRS 0x00200000

#define RAM_LOW_ADRS 0x00100000

TCP/IP通信实验

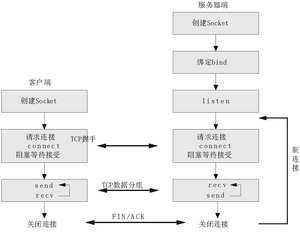

本文建立的实验环境包括:一块Virtex-II Pro开发板DS-BD-2VP20-FF1152(客户端),一台Pentium4计算机主机(服务器端),一根RS232串口线、网线,parallel IV下载线。基于TCP/IP的Socket应用框架原理如图4所示,经过实际测试得知,网络吞吐效率可超过30%。

图4 面向连接的Socket应用

客户端程序:

sFd=socket (AF_INET, SOCK_STREAM,0);

optval = 60000;

setsockopt (sFd, SOL_SOCKET, SO_SNDBUF, (char *)&optval, sizeof (optval));

sockAddrSize=sizeof (struct sockaddr_in);

bzero((char *)&serverAddr , sockAddrSize);

serverAddr.sin_family=AF_INET; serverAddr.sin_len=(u_char) sockAddrSize;

serverAddr.sin_port=htons (SERVER_PORT_NUM);

serverAddr.sin_addr.s_addr = inet_addr ("128.0.43.102");

connect(sFd, (struct sockaddr *)&serverAddr,sockAddrSize);

send (sFd ,(char *)&myrequest. message, REQUEST_MSG_SIZE,0);

服务器端的程序可以由VC类库来实现,这里就不再给出。

结语

开发基于FPGA的嵌入式系统是迈向最终SoC的必由之路,传统的FPGA厂商纷纷涉足嵌入式领域,FPGA所具有的低成本、低功耗、小尺寸、高性能、开发周期短等优势,必将使其在当今嵌入式开发的热潮中具有广阔的应用前景。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网