摘要:文中分析了红外线遥控器系统的数据编码和传输机制,并用VerilogHDL语言设计了基于FPGA的红外接收模块硬件电路,在VCS和VirSim仿真工具中进行了仿真测试;用XilinxISE 10.1软件进行了综合、适配和FPGA器件下栽测试,结果表明该电路实现了数据接收和显

示的目的,符合红外遥控数据传输协议。

关键词:红外通信协议;Verilog;FPGA

红外遥控技术已经在日常家用电器中得到了广泛应用,其使用方便、功耗低、抗干扰能力强的优点也越来越在智能仪器系统中受到重视。市场上的各种家电红外遥控系统技术成熟、成本低廉,但都是针对各自的遥控对象(彩电、冰箱、空调等),不能直接用于智能仪器。本文探讨了如何借鉴家电红外遥控系统的原理,自行设计解码电路,使智能仪器具有遥控功能。该模块是建立在遥控器内部使用的芯片为HS622 1的基础上的。红外接收头型号为IRM3638,输出为IR管脚。而该模块则是对IR的输出信号进行译码处理,并从中提取红外发射包中的有效数据,然后并行输出8位数据以及8位遥控器用户码(地址码)供别的模块调用。

1 红外接收控制模块设计原理

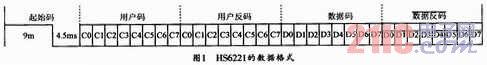

遥控器发射的信号由一串0和1的二进制代码组成。不同的芯片对0和1的编码有所不同,通常有曼彻斯特编码和脉冲宽度编码。HS6221的0和1采用PWM方法编码,即脉冲宽度调制,0码由0.56ms低电平和0.565ms高电平组合而成,脉冲宽度为1.125ms。1码由0.56ms低电平和1.69ms高电平组合而成,脉冲宽度为2.25ms。在编写解码程序时,通过判断脉冲的宽度,即可得到0或1。HS6221以及同类的芯片的数据格式包括引导码(起始码),用户码(地址码),用户反码(地址反码),数据码,数据反码,编码总共32位,数据反码是数据码取反后的编码,用户反码原理一样,可以用来对数据的纠错。具体格式见图1。

当按下遥控器的按键时。遥控器将发出如图1的一串二进制代码,称它为一帧数据。根据各部分的功能,可将它们分为5部分,分别为引导码、用户码、用户反码、数据码、数据反码。遥控器发射代码时,均是低位在前,高位在后。红外接收头会将高低电平变反,所以实际从IR端出来的电平是上述格式图中的波形取反,即停止状态时IR为高电平,然后接收到9ms左右的低电平后进入准备状态。由图中分析可以得到,引导码高电平为9ms,低电平为4.5ms,当接收到此码时,表示一帧数据的开始,FPGA可以准备接收下面的数据。用户码(地址码)由8位二进制组成,共256种,图中用户反码(地址反码)主要是加强遥控器的可靠性,不同的设备可以拥有不同的用户码(地址码)。因此,同种编码的遥控器只要设置用户码(地址码)不同,也不会相互干扰。在同一个遥控器中,所有按键发出的地址码都是相同的。数据码为8位,可编码256种状态,代表实际所按下的键。数据反码是数据码的各位求反,通过比较数据码与数据反码,可判断接收到的数据是否正确。如果数据码与数据反码之间的关系不满足相反的关系,则本次遥控接收有误,数据应丢弃。在同一个遥控器上,所有按键的数据码均不相同。

2 红外接收控制模块的HDL设计

2.1 红外接收控制模块功能简介

红外接收控制模块是基于遥控器内部使用的芯片为HS6221。在红外接收控制方面,抗干扰能力强、使用灵活。红外接收控制模块的功能包括消除时钟的延时、频率的合成、时钟相位的调整等系统方面的需求。红外接收控制模块的主要优点在于以下四点:

(1)实现红外数据译码功能,提取数据包中有效内容并并行输出;

(2)由于红外收发协议中利用了PWM协议,更加增强了数据的抗干扰能力;

(3)可以通过改变地址参数实现对不同地址发射器的接收;

(4)将数据包中的数据与数据包中的数据反码进行比较从而确保接收过程中没有出错。

对于红外接收控制模块来说,其关键参数为起始码、数据1、数据0的各自高低电平的脉宽以及本地地址等。

2.2 红外接收控制模块组成

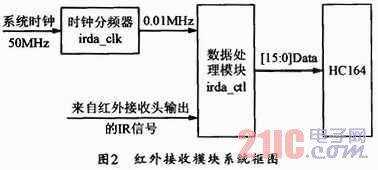

红外接收控制模块共由2部分组成,如图2所示。主要由时钟分频器和红外接收控制模块组成。图中的[15:0] Data是由8位数据以及8位地址组成。

2.3 红外接收控制模块各组成部分说明

时钟分频器:主要是将系统时钟(50MHz)分频成0.01MHz的时钟以驱动红外接收控制模块正常工作。PERIOD时钟分频模块的分频周期,当为15’d2500时分频得到周期为0.1ms的irda_clk时钟信号;仿真时候取15’d2是为了缩短仿真周期,减少工作量,产生周期为80ns的irda_clk时钟信号[2,3]。

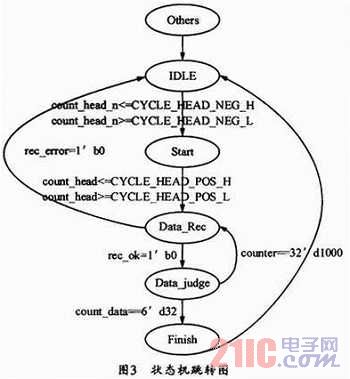

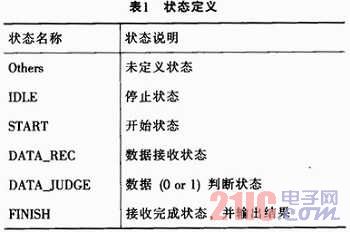

注意:同时只能取一个值,仿真用15’d2,下到FPGA时用15’d2500数据处理模块:该模块是红外接收控制模块的核心部分主要由状态机构成(FSM),如图3所示。

FSM各个状态说明如表1所列。

3 电路仿真、FPGA实现及应用测试

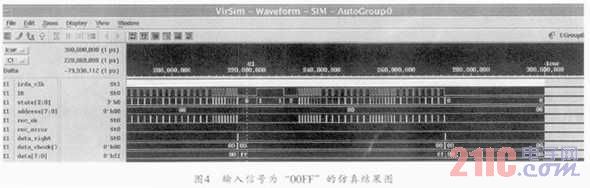

编写测试向量文件,在VCS和VirSim仿真工具中进行功能仿真,经检验完全符合设计要求。仿真结果图如图4所示。本设计的实现平台采用Xilinx公司的SPARTANIII OFP封装的XC3S400-4PQ208C,总逻辑门为400k门。经综合、适配、仿真、布局布线后仅占用比较少的器件资源。整个系统下载到FPGA后在50MHz时钟频率下能正常工作,在RM-139C超级版万能电视机遥控器遥控下,按下不同的按键,LED七段四位数码管经过译码后显示不同的按键遥控码。

4 结束语

用HDL和可编程逻辑器件(FPGA/CPLD)设计数字系统有传统方法无可比拟的优越性,它已经成为大规模集成电路设计最有效的一种手段。本文采用VerilogHDL设计了红外遥控信号接收模块电路。为简单起见,本设计中只对遥控传输的数据部分进行解码,不失一般性。本文提出的基于FPGA的红外遥控信号接收模块的设计方案经过电路仿真、FPGA实现及应用测试验证该模块完全符合红外遥控通信协议的要求。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网