1 概述

MPC860是基于PowerPC结构的通信控制器。它不仅是集成的微处理器,而且将很多外设的功能也集成在一起。MPC860具有存储控制器,其存储控制器的功能很强,可以支持各种存储器,包括各种新型的DRAM和Flash,并可以实现与存储器的无缝接口;而且使用嵌入式操作系统VxWorks和开发环境Tornado开发非常方便。

本设计中用1片Intel W28F1283A150 Flash作为BootFlash对MPC860进行加电配置,其多余的存储空间完全可以存放下FPGA所需的配置文件。加电复位、系统启动后,由MPC860处理机与EPLD配合,控制FPGA配置文件的下载过程,完成对FPGA的配置。使用MPC860可以对FPGA十分方便地进行配置,甚至可以通过MPC860的网络功能对FPGA进行远程配置,节省了因采用专用配置芯片所耗费的电路板及其成本。本文主要介绍如何用MPC860对Xilinx公司的Virtex II系列的FPGA进行配置,其原理同样适用于别的FPGA芯片(包括Altera公司)。

2 Xilinx FPGA的配置方式

本设计中FPGA采用Xilinx公司Virtex-II系列蝗XC2V4000,其配置文件的下载模式有5种:主串模式(master serial)、从串模式(slave serial)、主并模式(master selectMAP)、从并模式(slave selectMAP)、JTAG械。其中,JTAG模式在开发调试阶段使用。本设计将JTAG口直接做在信号处理板上,便于开发设计阶段的调试。

参考Xilinx公司的有关文档,比较其余4种下载模式,可将其分为串行下载方式和并行下载方式。串行下载方式和并行下载方式都有主、从2种模式。主、从模式的最大区别在于:主模式的下载同步时钟(CCLK)由FPGA提供;从模式的下载同步时钟(CCLK)由外部时钟源或者外部控制信号提供。主模式对下载时序的要求比从模式严格得多。因此从处理机易于控制下载过程的角度,选择使用从串模式或从并模式。本设计采用从串模式进行FPGA配置,以减少占用MPC860的资源。

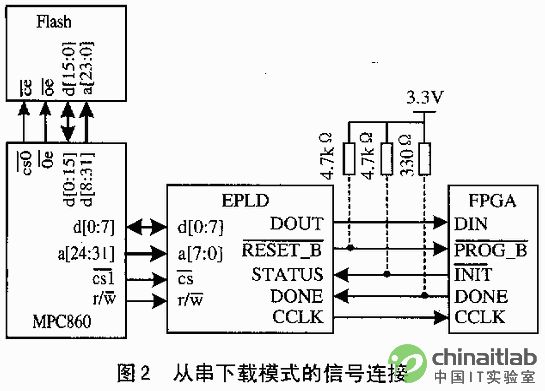

用MPC860对FPGA进行配置,实质上就是用MPC860和EPLD来仿真JTAG接口的下载时序,完成对 FPGA的下载。JTAG的有效引脚只有5个,分别是nConfig(PROG_B)、nStatus(INIT_B)、 Conf_Done(DONE)、DClk(CCLK)、Data0(DIN)。其中nConfig用于使FPGA进行到下载状态,nStatus时不否出现CRC校验错误,Conf_Done用于表示下载完成,而DC1k的Data则是用于在下载时产生时钟和数据位的。每一个CD1k时钟周期写入1个 bit数据(括号中标注为Xilinx的FPGA对该功能的称呼)。

表1所列为下载信号定义。

|

引 脚 |

方向(对FPGA) |

说 明 |

| Data0 |

输入 |

数据引脚 |

| DClk |

输入 |

同步时钟,由外部时钟源或控制信号提供 |

| NConfig |

输入 |

异步复位引脚,用于异步复位配置逻辑 |

| Conf_Done |

输出 |

配置状态 |

| nStatus |

输出 |

下载状态 |

引 脚 方向(对FPGA) 说 明 Data0 输入 数据引脚 DClk 输入 同步时钟,由外部时钟源或控制信号提供 NConfig 输入 异步复位引脚,用于异步复位配置逻辑 Conf_Done 输出 配置状态 nStatus 输出 下载状态

3 从串模式的配置信号和下载时序

(1)启动下载时序

在nConfig引脚上产生1个超过2μs的低脉冲,等待nStatus回应1个低脉冲以及Conf_Done。变低。这时候表明FPGA已经进入到了下载状态,等待至少5μs以后就可以开始下载了。

(2)下载时序

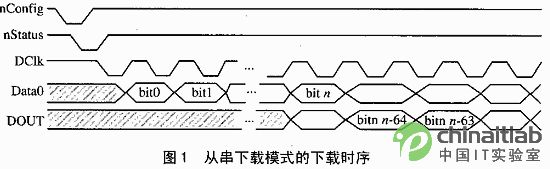

从串下载模式的下载时序如图1的所示。

在Data0上逐位地产生要下载的数据,同时在DC1k上产生时钟。数据必须在时钟的上升沿之间50ns有效,时钟高电平和低电平的时钟都不能小于80ns。这一过程一直持续到全部数据下载完成。在下载过程中可以出现相对较少时间的等待状态,而不会中断下载进程。如果发生错误,nStatus将被拉低,FPGA退出操作,必须重算1~3步骤。

(3)结束下载

在数据都下载完成以后,需要继续给FPGA提供若干的时钟,时钟要至少等到Conf_Done变高为止。

(4)启动器件

Conf_Done被释放,被外部拉高。

MPC860处理机控制从串下载模式的信号连接示意如图2所示。

4 MPC860下载模式的软件(状态机)设计

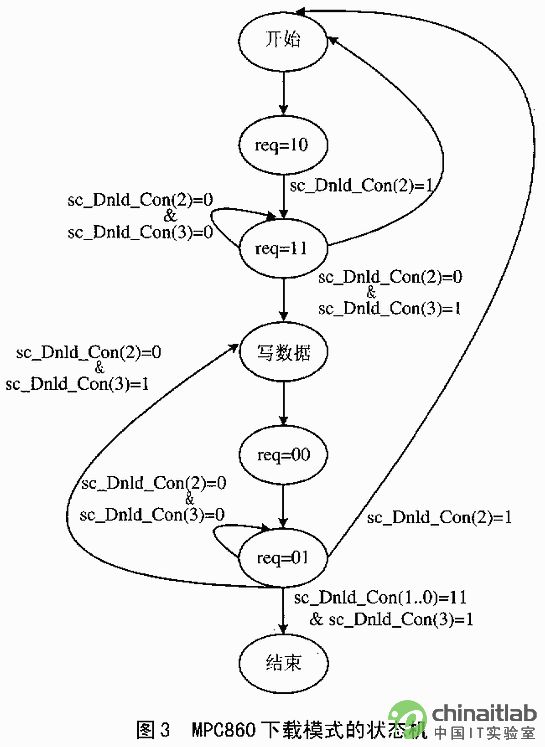

MPC860下载模式的状态机的实现是由PCM860处理器和EPLD协同来完成的。MPC860通过写入Sc_Dnld_Req(1..0)来控制状态机的下一个状态,通过判断EPLD中寄存器Sc_Dnld_Con(3..0)的内容来决定流程的跳转。

图3中状态req=“x”代表向EPLD的寄存器Sc_Dnld_Req写入数据“xx”。

其中,Sc_Dnld_Req(1 downto 0)使MPC860通过这个寄存器向EPLD发出指令,控制下载过程:

10——通知EPLD作好向FPGA发nconfig的准备工作;

11——通知EPLD开始向FPGA发出nconfig命令;

00——通知EPLD作好向FPGA下载数据的准备工作;

01——通知EPLD开始向FPGA逐位下载1个字节的数据。

如果下载过程顺序的话,第1、第2步只需在每次下载数据前进行1次,第3、第4步是每下载1个字节数据都要进行的步骤(每次写入下载数据的操作在第3步之前进行,且新数据要写入专门的寄存器Sd_Data_Byte(7 downto 0))。

Sd_Data_Byte(7 downto 0))是下载数据缓存。

Sc_Dnld_Con(3 downto 0)是4bit的只读寄存器。860通过查询这个寄存器的内容判断目标FPGA的当前下载状态,以决定应该发出什么样的指令。其各位代表的意义如下所述: ①Sc_Dnld_Con(3) ——为0时表示不可以发送新数据到EPLD,为1时允许发送数据;

②Sc_Dnld_Con(2) ——为0时表示工作正常,为1时表示下载过程中断;

③Sc_Dnld_Con(1) ——目标FPGA返回的nstatus信号;

④Sc_Dnld_Con(0) ——目标FPGA返回的conf_done信号。

结束语

MPC860有强大的资源,可以在外围电路不复杂的情况下实现Xilinx公司的FPGA的配置程序下载。本设计经过实际调试,已成功地用于所开发的数字通信信号处理板上,效果良好。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网