随着芯片规模的越来越大、资源的越来越丰富, 芯片的设计复杂度也大大增加。事实上, 在芯片设计完成后, 有时还需要根据情况改变一些控制, 这在使用过程中会经常遇到。这时候如果再对芯片设计进行改变将是很不可取的, 因为需要设计人员参与这种改变, 这无论是对设计者还是用户都是不能接受的。于是就有必要让这种可以改变的简单控制在芯片设计时就存在, 而且同时还应该使这种改变相对容易, 比较通用, 并且与芯片的其它设计部分尽量不相关。为了满足上述的要求, 在FPGA中嵌入一个比较理想的选择, 而这个即通用又控制简单的IP核最好选择8051微处理器。

在FPGA中植入8051后, 还可在上面实现简单的TCP/IP协议, 以支持远程访问或进行远程调试, 这只是在嵌入FPGA的8051上的一个应用。为了保证用户能够对8051实现不同的控制操作,设计时也可以采用一个外部flash对8051进行加载, 这样, 用户只需要将编译好的汇编语言代码加到flash就可以控制8051的工作, 而此时用户完全不需要对FPGA进行操作就能实现简单的控制,而这需要的仅仅只是keil的编译环境。

1 IP核8051的FPGA实现

现在有许多免费的8051核可以利用, 这些核都可通过硬件描述语言来实现, 并且基本上都可综合, 也就是直接拿来就能用, 需要的只是根据自身的具体需求做一些简单修改即可。总的说来, IP核8051的移植是比较简单的。

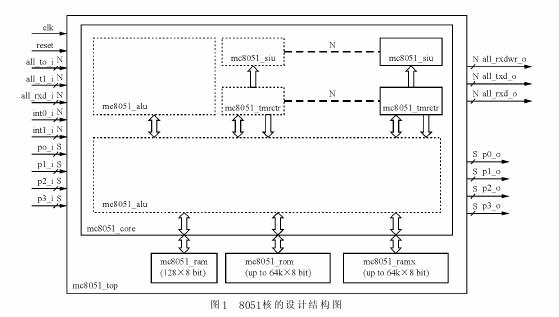

本系统的设计与实现可以采用oregano system的mc8051内核, 并且加入定时计数的和串口模块, 8051单片机的设计结构框图如图1所示。

在8051核的FPGA设计中, 完全可以实现包括计时/计数、中断、串口、数据及程序存储器、特殊寄存器、布尔处理的位处理机等的所有功能, 而且兼容所有指令, 只是在具体的移植过程中做一些改变而已。

这种方法对程序存储器不再做内外之分, 因为FPGA内部存储容量已经能够满足要求, 同时将程序存储器的容量扩大了一倍 (变为8KB), 以满足大程序的容量需求; 为了让8051更为强大且更具有通用性, 可将数据存储器RAM的容量扩大一倍, 变为256字节。可以看出, 在设计过程中将8051的功能也进行了加强, 但是并不影响对它的控制, 仅仅是在硬件上对存储器的容量进行了扩大, 而这种扩大只是改变了地址线的宽度, 完全不影响111条指令的正确执行。对用户来说这只是可以使用的内部RAM增加了, 控制并没有任何改变。当然, 在资源比较紧张, 而且程序容量比较小时, 也可以将存储器的容量改小, 这种改变也相当方便, 只需要改变地址线的宽度就能达到目的。由此可见, 设计时完全可以根据需要改变IP核的设计, 而不局限于8051。

虽然整个8051IP核能正确执行所有指令, 并能实现串口、计时器及中断控制, 且整个IP的核工作时钟也在20 MHz以上, 但是, 由于这时候的所有指令周期并不与真实的8051完全一致, IP核中有的指令需要比真正的8051多执行几个周期才能完成, 这就使得分析IP核的工作时钟复杂起来了, 因为相对于真正的8051不能有一个精确的工作时钟对比。但是经过分析仍然可以认为, IP核应该可以工作在15 MHz左右, 也就是比真实的8051快了15倍左右。这对于芯片整体来说, 其速度可能相对较低, 但是由于这部分与芯片其它部分的逻辑相关性极小, 所以并不会影响芯片的整体性能, 而对于一些简单控制来说, 这个速度还是能够满足要求的。

2 UIP协议栈

2.1 UIP简介

在FPGA中实现TCP/IP协议的主要目的是为了满足设计人员对芯片的远程调试。而满足这种要求实际上并不需要很强大和快速的传输功能。功能过于强大将会占用过多的资源, 而且实际上, 很多功能并没有实际作用; 同时也不需要很快的传输速度。毕竟对于一个芯片的设计来说,无论是设计文档或是设计程序, 容量都是非常有限的。综合考虑, 则应选择一个实现简单、占用资源少, 但能够比较稳定地进行数据传输的协议, 为此, 本文选择了相对简单的UIP协议栈,而放弃了功能比较强大的LWIP协议栈。选择UIP还有一个好处, 就是这个协议栈是专门针对单片机等微控制器设计的TCP/IP协议栈, 它能够利用嵌入的IP核8051来实现TCP/IP协议, 而不再需要额外的逻辑单元。

UIP的特点是代码量和数据量都比较小, 因而可以为存储器比较紧张的地方提供合适的实现方案, 包括TCP/IP所需的最小实现方案和只包含TCP、IP、ICMP (ping) 以及简单的UDP协议, 其具体的实现方法如图2所示, 图2中, 带“×”的表示已经实现。

2.2 UIP协议栈的实现方法

通过UIP可实现TCP/IP协议集的四个基本协议, 包括ARP地址解析协议、IP网际互联协议,ICMP网络控制报文协议和TCP传输控制协议。为了在8位、16位处理器上应用, UIP协议栈在实现各层协议时采用有针对性的方法来保证代码大小和存储器使用量最小。

实现ARP地址解析协议时, 为节省存储器,ARP应答包可直接覆盖ARP请求包; 而在实现IP网络协议时, 则对原协议进行了极大的简化, 并没有实现分片和重组; 当实现ICMP网络控制报文协议时, 只需实现echo (回响) 服务。UIP在生成回响报文时, 并不重新分配存储器空间, 而是直接修改echo请求报文来生成回响报文。设计时可将ICMP类型字段从“echo”改变成 “echo re-ply”类型, 并重新计算校验和修改校验和字段。UIP里的TCP没有实现发送和接收数据的滑动窗口。每个TCP连接的状态均由uip_conn结构保存。uip_conn结构包括当地和远端的TCP端口编号、远程主机的IP地址、重发时间值、上一段重发的编号以及连接段的最大尺寸等信息。uip_conn结构数组可用于保存所有的连接, 数组的大小等于可支持同时连接的最大数量。为了减少储存器的使用量, 在处理重发时, UIP并不缓存发送的数据包, 而是由应用程序在需要重发时重新生成发送的数据。

2.3 UIP协议栈的接口

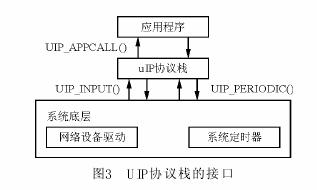

为了UIP协议栈能具有最大的通用性, 在实现时可将底层硬件驱动和顶层应用层之外的所有协议集“打包”在一个“库”里。协议栈通过接口与底层硬件和顶层应用进行通信。通过这种方式可使uIP具有极高的通用性和独立性, 以便移植到不同的系统和方便地实现不同的应用, 很好的体现TCP/IP协议平台无关性的特点。UIP协议栈与系统底层和应用程序之间的接口如图3所示。图中, 各接口之间都是由一系列函数来实现的。

3 UIP协议栈在IP核8051上的实现

3.1 UIP协议栈在IP核8051上的移植

由于UIP协议栈是专门针对微处理器编写的,所以移植也是非常的方便, 但需注意以下几点:

(1) 协议栈是用C语言编写的, 故在移植时需要再加上两个头文件, 一个是8051的头文件, 另一个是8051的硬件初始化头文件;

(2) 通过keil c编译器编译时, 在选器件时需要注意, 只有选取数据寄存器为256个字节才能顺利通过编译, 这也是为什么前面8051IP核的数据存储器RAM需要扩展至256个字节的原因。不对RAM进行扩展, 就会出现“不能写B9地址”的错误, 因为在没有对RAM扩展前, 根本不存在B9地址;

(3) 将软件keil编译生成的hex文件送入到8051的程序存储器, 即可在IP核8051上实现简单的TCP/IP协议。这在软件测试时, 与实际工作将有所不同。软件测试时需要将hex文件作为程序存储器的初始化输入, 即在EDA软件编译8051时, 将程序存储器的初始化文件mif的路径设置为hex所在的路径, 在完成综合布线后, hex文件的内容就进入了程序存储器。这样, 仿真时就能在8051IP上实现TCP/IP协议了。

3.2 UIP的工作流程

TCP/IP协议在嵌入到FPGA的IP核8051上的工作流程, 实际上也是简化后的TCP/IP协议的工作流程, 这跟正式的TCP/IP协议有所不同。下面的工作流程以输入一个同步帧 (即: 三向握手的第一次握手) 为例。对于8051实现的UIP来说, 它属于被动建立连接, 其正确的输出结果应该是三向握手的第二次握手, 送出一个确认同步帧是所期望的结果。

下面简单介绍UIP的整个工作流程:

(1) 在P0端口有数据前, 读取数据函数并反复执行, 以对P0端口进行监视 (此种情况只是在测试时, 实际工作中物理层通过控制信号通知读数函数P0口是否有数据);

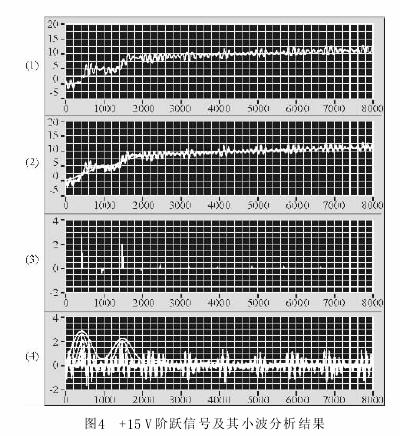

(3) 为信号的第8级分解小波模极大值图; (4) 为信号各级 (共9级) 的高频分量即小波系数。

由图4可以看出, 该故障信号分析仪能有效采集实时故障信号, 并可在对信号经过小波分析后有效的提取故障特征, 而且故障点定位明显。

5 结束语

该便携式接触网故障信号分析仪采用图形化程序设计语言LabVIEW开发设计, 可实现数据的高速实时采集、在线分析、自动存储、显示等功能。高速数字化仪NI PXI- 5112卡采样速度高、性能稳定可靠, 适宜对高速变化信号的实时监测。将软件安装在PXI- 1042工控机上, 具有体积小、抗干扰能力强、携带方便等特点, 同时具有故障性质判断、故障定位功能。该系统目前已经在石家庄变电所现场运行, 效果良好。

参考文献

[1] 刘君华.基于LabVIEW的虚拟仪器设计[M].北京: 电子工业出版社,2003:115- 127.

[2] Rober H. Bishop.LabVIEW6i 实用教程[M].北京: 电子工业出版社,2003:209- 265.

[3] LabVIEW Data Acqusition Basics Manual on NI- 5112[M].National Instrument Corpration,1998.

[4] Mok Aloysius K,Srusrt Douglas.RTT seman tics forLabVIEW.IEEE Aerospace Applications ConrerenceProceedings,1998:61- 71.

[5] 杨乐平, 李海涛,等.LabVIEW高级程序设计[M].北京:清华大学出版社,2003:390- 392.

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网