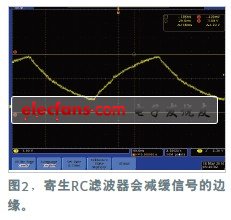

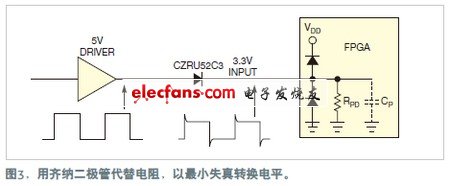

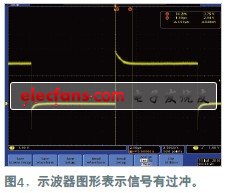

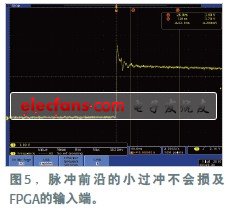

虽然5V电源逻辑在很多应用中仍很常见,但大多数FPGA都支持3.3V以及更低的接口电平。FPGA应用说明通常建议,当把一只FPGA连接到较高电压电平时,FPGA的I/O块中要用PCI(外设部件互连)总线箝位二极管,并外接一只串联限流电阻,以防止损坏FPGA(图1)。PCI箝位二极管会将电压限制在不致损坏输入端的电平,而电阻则将电流限制在一个不会损害PCI箝位二极管的安全水平。这种方案在低速信号的设计中工作良好。 不过,当将此方案用于较高速率信号时,寄生RC滤波器的效应就会使信号失真(图2)。FPGA应用说明中的电路需要做个变动,无需重新设计PCB(印刷电路板)就可以完成这个变动。本例用一只齐纳二极管替代了电阻,用于转换信号电平,而不会造成明显的失真(图3)。齐纳二极管与PCI箝位二极管和内部上拉电阻一起工作,设定了输入端的电压电平。 要设定输入端的静态电平,必须使能FPGA的内部上拉电阻,以防止当输入端持续为高时,PCI箝位二极管被过度驱动。上拉电阻的电流小于齐纳二极管的额定电流。另外,低压齐纳二极管的雪崩IV(电流-电压)曲线中还有圆滑的“拐点”(knee)。 此曲线表明齐纳电压低于额定值,因此需要使用一个较高电压的齐纳二极管。二极管还应有小的电容。Comchip公司的CZRU52C3是一只3V的齐纳二极管,它能正常工作,使电路电压降低2V(图4)。 齐纳二极管中的某些寄生效应会给波形带来其他失真。二极管有寄生电容,它使二极管开始看似与5V驱动器的信号沿有一个短路。FPGA管脚会看到一个大约10 ns的高压过冲,快速地衰减到输入脚的额定电平。管脚电容与下拉电阻的RC时间常数产生一个到最终值的较慢下降,速率由齐纳二极管和下拉电阻所决定。图5给出了前沿的详图。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网