国外电子元器件 张时华 任勇峰 李圣昆 刘鑫

1 引言

某飞行器发射前,需测试飞行器各项参数,参数测试是通过数据记录器记录飞行器数据并传至地面测试台。测试过程中,为了保证测试人员人身安全,飞行器和地面测试台间距需有300 m,两者间采用长线数据传输。现有的技术有:RS一485总线,在几百米时,传输速度较低;CAN总线虽具有较高的可靠性,但传输速度也较低;而千兆以太网接口的传输速度很快,但以太网协议复杂,不适用。为此,这里提出一种基于FPGA和LVDS接口器件的光缆传输技术。

2 LVDS简介

低电压差分信号(Low Voltage Differential Signaling,简称LVDS)是一种适应高速数据传输的通用点对点物理接口技术。它采用低摆幅差分信号技术,使其信号能在差分PCB线对儿或平衡电缆上以几百Mb/s的速度传输.其低摆幅和低电流驱动输出实现低噪声和低功耗。

每个点到点连接的差分对儿由驱动器、互连器和接收器组成。驱动器和接收器主要完成TTL信号和LVDS信号之间的转换。互连器包含电缆、PCB上差分线对儿以及匹配电阻。LVDS驱动器由一个驱动差分线对儿的电流源组成,LVDS接收器具有高输入阻抗,因此驱动器输出的电流大部分都流经100Ω的匹配电阻,并在接收器的输入端产生约350 mV的电压。当驱动器翻转将改变流经电阻的电流方向,因此产生有效的逻辑1和逻辑O的低摆幅驱动信号实现高速操作并减小功耗,差分信号提供适当噪声边缘。不管使用的是PCB线对儿还是电缆,都必须防止反射,减少电磁干扰。LVDS要求使用一只与介质相匹配的终端电阻,应将其尽可能地靠近接收器放置。LVDS接收器可以承受1 V的驱动器与接收器间对接地的电压差。由于LVDS驱动器典型的偏置电压为1.2 V,所以其电压差驱动器典型的偏置电压以及轻度耦合噪声之和范围为0.2~2.2 V。建议接收器的输入电压范围为0~2.4 V。

3 总体设计方案

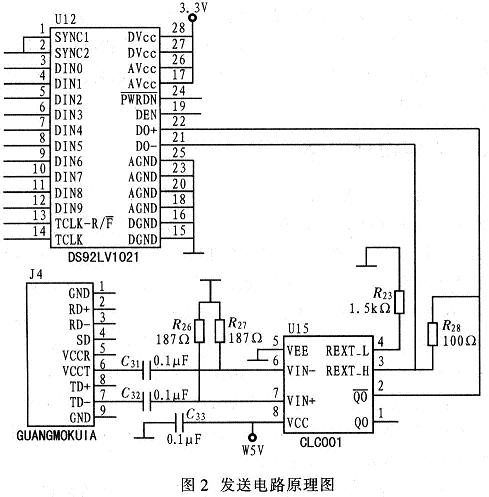

系统设计要求传输速度应在1~16 Mb/s自动适应,传输距离不小于300 m,且必须与其他系统电磁隔离,避免电磁干扰。因此,该系统设计采用集成的LVDS接口器件DS92LVl021,其数据传输速度是16~40 Mb/s,10位数据位。而CLC001,CLC012为专用长线电缆驱动器,与光模块相结合可将传输距离扩展2 km,且外部电路简单,功耗低。FPGA选用Spartan一2系列器件,其最高工作速度为200 MHz,逻辑宏单元丰富,满足系统设计要求。因此,该系统设计选用LVDS接口器件实现LVDS长线传输,而记录器、测试台和LVDS器件接口的时序匹配则选用FPGA实现。

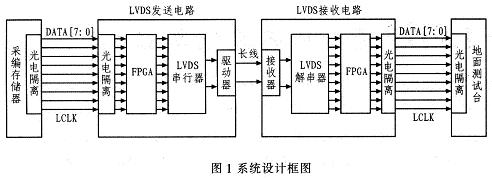

图1为系统设计的框图,测试台发送的STATE、CTLl、CTL2等状态及控制信号传送至记录器,并将记录器发送的数据及同步时钟传送至地面测试台。其中,记录器、LVDS发送端、LVDS接收端的电源均由测试台提供,电压为+9 V。

LVDS长线传输模块分为LVDS发送电路和LVDS接收电路。LVDS发送电路将从记录器接收到的并行数据进行速度匹配后转换成LVDS串行数据流,并通过双绞线发送。LVDS接收电路将接收到的LVDS串行数据流还原成并行数据进行速度匹配后送至测试台。

4 硬件设计

该系统设计的关键部分为LVDS的接口设计,由于传输数据速度很高,因此应按照高速电路的要求进行设计,所有布线应尽量短,传输线路阻抗匹配。传输模块发送端工作时首先由FPGA给DS92LV1021的使能端DEN及TCLK-R/F触发沿选择高电平,并向TCLK引脚输出20 MHz的工作时钟,接着DS92LV1021将从FPGA处接收到的TTL并行信号转换为LVDS标准的串行信号,再由Do一及Do+输出至CLC001驱动器,经电光转换后,由光缆传输至接收板电路,并由接收电路的光电

传输模块接收端主要由CLC012均衡器及DS92LV1212解串器组成。DS92LV1212的D00~D09将还原出的并行数据输出,RCLK为还原出的同步时钟,REFCLK为解串器的工作时钟,由FPGA给出。

5 软件设计

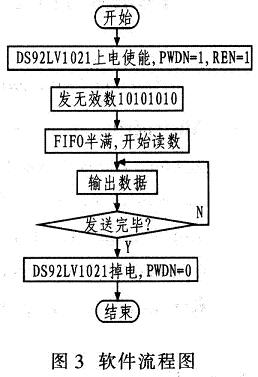

系统上电后,测试台先向采编器发出读数命令,采编器接到命令后,以l Mb/s的速度输出8位并行数据,而LVDS传输器件最低工作速度为16 Mb/s,为了实现速度匹配与自适应,该系统设计采用了Soatan-2E型FPGA内部双口RAM实现FIFO,其时钟最高工作频率为200 MHz,满足要求,当采编器以1 M b/s速度输出数据时,首先进入FPGA内部FIFO,FPGA内部对数据计数,当存满512个数后,FPGA以20 Mb/s的速度输出8位并行数据,为了保证DS92LVl021一直处于工作状态,FPGA在两次发送数据的间歇所输出的无效数,有效数和无效数通过LVDS传输器件的lO位数据位的高2位数据位作为标志位进行区分,在接收端FPGA通过判断标志位来识别有效数或无效数,舍弃无效数,保证数据正确传输。FPGA在整个系统中起数据缓冲作用,由于采用FIFO作为外部数据接口,所以可实现对外部数据的自适应要求。整个程序用VHDL语言编写,流程图如图3所示。

6 试验结果

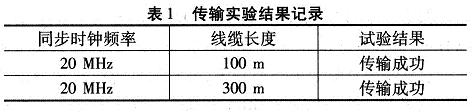

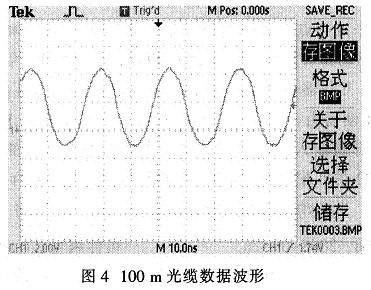

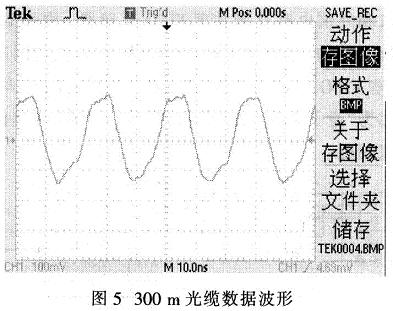

为了测试最终效果,在发送电路和接收电路之间用不同长度的单模光纤连接,系统上电后,发送端发送数据速度为20 Mb/s,使用示波器捕获接收端数据波形,并进行对比,实验结果记录如表1所列。图4和图5分别给出100 m和300 m光缆的数据波形。由数据波形图知,在传输过程中,波形畸变非常小,没有出现误码和丢数的现象,完全满足系统要求。

7 结语

本文所述LVDS长线传输方案具有电路设计简单,传输速度快,传输距离远的优点,并且对传输速度能够自适应,在需远距离传输的环境中有广阔的应用前景。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网