教你使用PlanAhead进行 I/O Pin Planning

发布者:jackzhang

时间:2011-10-09 21:59:35

转自:21IC 赛灵思FPGA世界 作者:金猴

声明:本教程为Goldsunmonkey为庆祝Xilinx论坛成立一周年来与大家分享一些东西的系列。

为Xilinx和Xilinx论坛发展贡献自己的一点力量。可以供大家(除商业意图以外)随意下载使用交流。

如果使用为了商业意图,请联系作者。

兄弟姐妹们对使用PlanAhead有很多抵触,其实是不了解PlanAhead强大功能,现在就想和大家一起分享Xilinx的PlanAhead的I/O Pin Planning

教程使用的工具:

ISE 13.2

XILINX 开发板 SP605

实验材料为UART_LED的材料

教程的目的

教会大家使用Xilinx PlanAhead的界面

教会大家使用Xilinx PlanAhead的工具进行IO管脚分配基本操作。

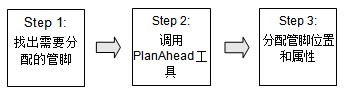

教程的流程

寻找需要分配的管脚: 1. 根据SP605的

硬件数据手册ug526(见附件),找出12个管脚的合适位置。

1,1

学习附件中design_descript_uart.rar的材料中关于Uart_led

设计的描述。

填好下表。

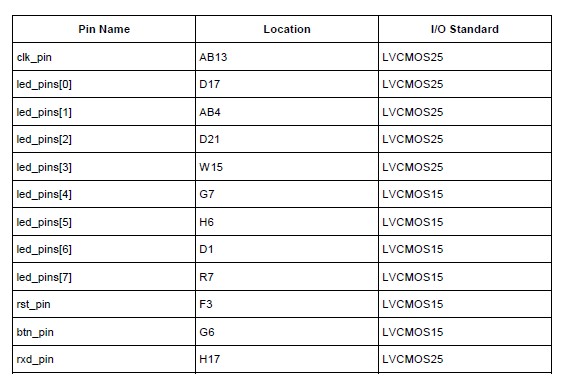

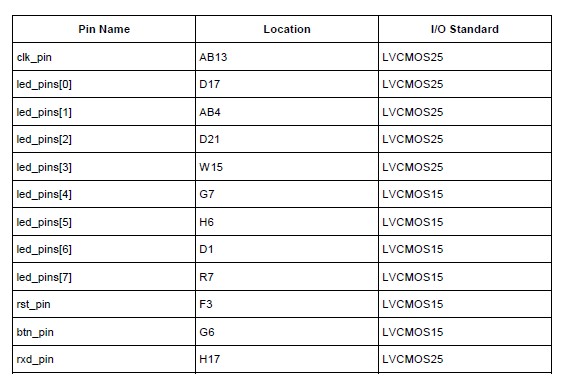

1.2 从ug526中找到

SP605 Evaluation Board > Detailed Description >

Clock Generation >Oscillator Socket部分。从中找到27MHZ时钟的位置,

把他分配给Uart_LED时钟管脚

1.3从ug526中找到

SP605 Evaluation Board > Detailed Description

> User I/O > User LEDst部分。把里面的LED等的位置分配给UART-LED的灯0~3

1.4从ug526中找到

SP605 Evaluation Board > Detailed Description

> User I/O > User SIP Header部分。把里面的GPIO_HEADER_0-3的位置分配给UART-LED的灯4~8

1.5从ug526中找到

SP605 Evaluation Board > Detailed Description

>

USB-to-UART Bridge部分。

把里面的USB_1_TX的位置分配给UART-LED的rxd_pin

1.6从ug526中找到

SP605 Evaluation Board > Detailed Description

> User I/O > User PushButtonSwitches部分。

把里面的GPIO_BUTTON_0 andGPIO_BUTTON_1的位置分配给UART-LED的rst_pin和btn_pin

1.7从ug526中找到

SP605 Evaluation Board > Overview > Block Diagram部分。

如果我们分配的管脚bank

电压都为2.5v电压,那么我们应该添上电压标准LVCMOS25.

如果我们分配的管脚bank电压都为1.5V电压,需要填电压标准为LVCMOS15.

那我们得到如下的表格:

调用PlanAhead工具:

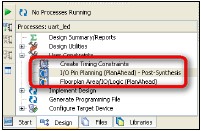

调用PlanAhead工具: 2.1 双击试验材料中的uart_led.xise

2.2 双击调用the PlanAhead tool in I/O pin planning 模式

2.3 关闭PlanAhead欢迎窗口,PlanAhead将和design netlist 和 constraints file 一起被打开。

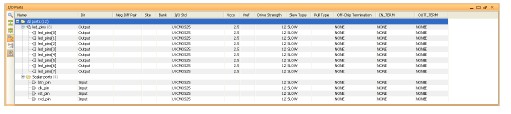

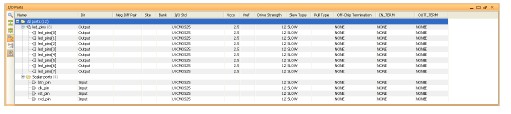

2.4 展开IO PORTs窗口,检查所有管教的

设置是否和我们所列的表格一致。

显然不一致,必然要开始我们的第三步调用PlanAhead工具进行管脚分配和属性设置:

显然不一致,必然要开始我们的第三步调用PlanAhead工具进行管脚分配和属性设置: