一个拥有69万逻辑单元的很大规模的器件,里头的资源非常多,包括收发器,可以实现100兆的带宽。要做这样的一个设计,只要做一次布局布线,假如用原来老的传统的开发工具,每做一次要23个小时,而用Vivado工具,3个小时左右就可以做完。这就是赛灵思打造的“All Programmable”器件全新工具的优势之一。

一个面向新一代的设计工具

Vivado设计套件将大幅提升当今设计的生产力,且能够轻松实现升级扩展,应对20nm芯片及更小工艺技术所带来的容量和设计复杂性挑战。

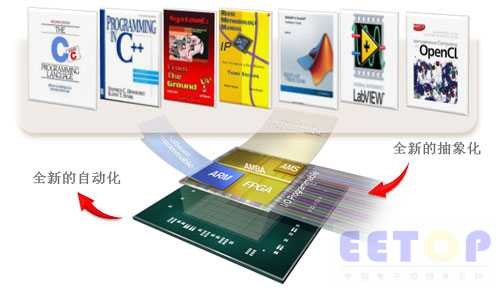

自计算机的计算诞生以来,抽象与自动化已成为设计团队提高生产力的有力工具。为了满足市场要求,设计团队正在借助软硬件设计方法,并利用具有不同抽象层次的异构并行架构来开发更智能系统。行业标准与开源社区的推广使抽象自动化成为可能。就硬件加速而言,IP标准正在孕育着真正的即插即用型IP,并促进IP集成自动化发展,从而有助于提高设计人员的设计生产力。

Vivado设计套件配合使用广泛的第三方操作系统、工具和IP核,可加速All Programmable器件的集成与实现,开辟设计自动化之路。

IP集成器

最新发布的Vivado设计套件提供一种新型IP集成器(IPI),用于实现IP智能集成。IPI提供图形化、脚本编写(Tcl)、生成即保证正确(correct-by-construction)及以IP和系统为中心的设计开发流程。IPI建立在Vivado集成设计环境的基础之上,同时具备器件感知与平台感知功能。这种互动环境支持关键IP接口的智能自动连接、IP子系统一键式生成、实时DRC以及接口变更传播功能,而且具备强大的调试功能。

IPI使设计可以通过“生成即保证正确”的方式完成。设计人员能够进行接口级抽象(interface level of abstraction),并可利用广泛的IP系列。这些IP通过AMBA AXI4接口提供,存储在一个开放的行业标准IP-XACT库中。设计团队现在可以使用IPI快速组装复杂的系统。将该工具与其他Vivado功能配合使用,能够确保设计和IP得到正确配置,因此利用VHDL或Verilog语言提高以上抽象,从而改善生产力。

高层次综合

传统的标准软件抽象现在也被用于硬件开发。很多开发团队将C和C的派生语言作为硬件开发的建模语言。主要原因有两点:这种方法的验证优势是RTL仿真的100倍;或开发团队需要对运行在处理器上的算法进行加速。Vivado高层次综合能使赛灵思All Programmable器件充分满足C、C++和System C规范要求,从而加速IP的创建。Vivado HLS无需手动创建RTL,同时还能提供快速的设计空间探索。由于能够提高生产力和设计重用性,这种工具正在得到广泛应用。

赛灵思通过推出最新的Vivado,为具有行业标准的OpenCV库增添了有效支持。OpenCV可帮助优化运行在处理器(例如Zynq-7000 All Programmable SoC上的处理)上的智能视频算法移植到基于硬件的加速器上(该加速器可通过IPI快速集成到异构系统中)。凭借Vivado IPI与HLS系统,设计架构师就可以更加快速地实现复杂的异构系统。

自动化而非指令性的设计流程

根据解决问题的要求不同,开发团队也会采用基于模型的抽象。基于模型的流程可提供一系列面向智能视觉、智能网络应用及其他应用的丰富模型库。设计团队可以开发并改善算法,在更高的抽象级别上充分满足系统要求,且无须担心具体的实现细节。然后,基于模型的流程会自动从算法模型中生成用于处理器的C代码以及RTL代码。

要想充分发挥All Programmable设计的优势,主要取决于自动化水平和高层次的抽象。今天,赛灵思率先推出各种设计方法,能充分应对上述挑战。赛灵思与其生态系统的联盟成员共同开发并推出直观的智能标准化设计流程,可支持开发工作实现自动化(而非指令化),从而在确保性能、功耗或成本优势的前提下灵活地满足开发团队的需求。

面向未来打造

Vivado是为面向未来5到10年的All programmable器件设计而打造,但Vivado的开发流程及工具并非未来的产品。Xilinx在2011年就已经开始为早期客户提供支持。2012年正式上市量产,使用下来,客户能直接获得设计生产力及设计质量(QOR)大幅提升的好处,其中包括:

首先是基于C语言和标准的IP集成,它将现有的C/C++算法验证速度提升100倍之多,C到验证的RTL时间加速4倍,RTL仿真时间大大缩短至原来的1/3,IP复用和IP集成的时间加速4倍

其次是分层次的设计流程和先进的时序收敛自动化,将设计时序收敛加速4倍,增量ECO时间缩短,仅为原来的1/3,相对同类竞争解决方案而言,其LUT利用率提高了20%以上。

最后是这些设计资源和生产力优势,给客户带来了快达3速度等级的性能优势(可以用同样器件速度等级低一些的器件满足更高系统性能的需求),节省功耗平均35%,上市速度加快4倍。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网