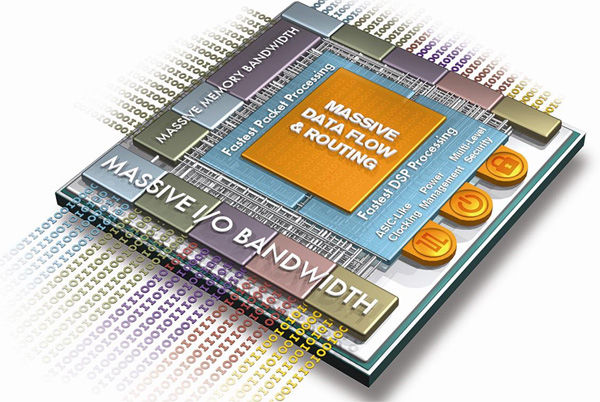

近日,可编程器件领导厂商Xilinx发布了两则对于半导体业来说相当重要的消息:一是首款20nm FPGA投片,这是除英特尔外首个在第三方代工厂投片的20nm高端芯片;而另一个我认为更重要的是Xilinx宣布采用了一种全新的架构——UltraSCALE,在FPGA中加入重要的ASIC技术,并会按重要客户的需求来预设计,这是直指ASIC/ASSP最核心的极高端应用,这可能带来一次业界在高端芯片的重组与洗牌。

Xilinx这个大变革的背后是,谷歌、Facebook、腾讯、百度和阿里等互联网大数据公司都开始寻求自已定制核心芯片,而不会购买标准的商业芯片,因为他们的最核心的竞争力就在数据信息的把控。FPGA中加入重要的ASIC技术,突破了传统FPGA在系统吞吐量上的瓶颈,但是又比ASIC灵活,研发速度快,这种全新的架构将受到这些互联网大数据巨头的青睐。当然,除了这些互联网巨头外,传统的设备厂商也需要快速定制网络核心的芯片,因为他们的客户——电信运营商/网络运营商也需要大量定制,但是传统ASIC的方式在半导体工艺进入20nm后,没有量的支持成本根本无法负担,所以,这种FPGA中融入ASIC的方式正好满足了新形成下的需求。

赛灵思对UltraScale架构进行了数百项设计提升,加入重要的ASIC技术

全新UltraScale架构中加入了哪些类似ASIC的功能?

UltraScale架构在完全可编程架构中应用尖端的ASIC技术,能从20nm平面FET扩展至16nm FinFET甚至更先进的技术,并可从单芯片电路扩展为3D IC。UltraScale架构不仅可以解决传统FPGA系统总吞吐量扩展和时延方面的局限性,而且还能直接突破高级节点上的头号系统性能瓶颈,即互连问题。它是如何实现的呢?

首先,提供了类似ASIC的时钟功能。

UltraScale架构中可提供类似ASIC的多区域时钟功能,使得设计人员现在可以将系统级时钟放在整个晶片的任何最佳位置上,从而使系统级时钟歪斜降低多达50%。将时钟驱动的节点放在功能模块的几何中心并且平衡不同叶节点时钟单元(leaf clock cell)的时钟歪斜,这样可以打破阻碍实现多Gb系统级性能的一个最大瓶颈。UltraScale架构的类似ASIC时钟功能消除了时钟放置方面的一切限制并且能够在系统设计中实现大量独立的高性能低歪斜时钟资源,而这正是新一代设计的关键要求之一。这是与前几代可编程逻辑器件所采用的时钟方案的最大不同之处,而且实现了重大改进。

其次,提供了新一代路由:以应对大数据时代网络中心的海量数据流挑战。

对于海量数据流、多Gb智能包处理、多Tb吞吐量以及低时延方面的要求,互连问题已成为影响系统性能的头号瓶颈。

我们来做个类比。位于市中心的一个繁忙十字路口,交通流量的方向是从北到南,从南到北,从东到西,从西到东,有些车辆正试图掉头,所有交通车辆试图同时移动。这样通常就会造成大堵车。现在考虑一下将这一十字路口精心设计为现代化高速公路或主干道,情况又会如何。道路设计人员设计出了专用坡道(快行道),用以将交通流量从主要高速路口的一端顺畅地疏导至另一端。交通流量可以从高速路的一端全速移动到另一端,不存在堵车现象。下面的两幅图说明了这一观点:

赛灵思为UltraScale架构加入了类似的快速通道。这些新增的快速通道可供附近的逻辑单元之间传输数据,尽管这些单元并不一定相邻,但它们仍通过特定的设计实现了逻辑上的连接。这样,UltraScale架构所能管理的数据量就会呈指数级上升,如下图所示。

通过UltraScale架构提供的高布线效率从根本上完全消除了布线拥塞问题。结果很简单:只要设计合适,布局布线就没有问题。这样也使器件利用率达到90%以上,且不降低性能或增加系统时延。

第三,实现了快速、智能的处理

从噪声中提取更多信号,创建更加逼真的画面,以及应对无止境的数据包流量增长,所有这些都在对智能处理性能提出更高要求。与此同时,还要将成本控制在规定的预算范围内,这样就给设计带来了诸多实际限制。简言之,市场需要以更少的成本实现更高的系统性能,这是大多数电子产业永恒不变的趋势。

UltraScale架构最新的27x18位乘法器和双加法器以及关键路径优化功能显著提升了定点和IEEE 754标准浮点算法的性能与效率。UltraScale架构能够让双精度浮点运算的资源利用率实现1.5倍的效率提升,并具有更多的DSP资源数量,因此可以满足新一代应用在TMAC处理性能和集成方面的要求,并实现最优价格点。

UltraScale架构经过专门优化,可解决以数百Gbps速率运行的包处理功能有关的关键路径瓶颈问题,这些功能包括:误差校正与控制(ECC)、循环冗余校验(CRC)以及前向纠错(FEC)。增强型DSP子系统,与硬化的100 GbE MAC和Interlaken接口以及赛灵思SmartCore 包处理与流量管理IP完美结合在一起,采用最佳封装,能够实现线速高达数百Gbps的包处理功能。

第四:努力满足新一代系统的系统级功耗要求

建立在原有低功耗All Programmable逻辑器件之上,UltraScale架构通过半导体工艺以及通过芯片与软件技术实现的宽范围静态与动态电源门控还可将系统总功耗降低至赛灵思7系列FPGA(业界最低功耗的All Programmable器件)的一半。

图:采用UltraScale架构实现最低总功耗

降低功耗对设计人员来说意味着两件事:(1)更低的功耗预算和散热管理要求;(2)更高的速度。这两点对满足新一代应用不断提高的要求极为重要。

综上所述,全新的FPGA+ASIC架构,与之前的固化在FPGA中的一些加速器完全不同,它是对整个架构的改革。新一代基于UltraScale架构的FPGA将会迎接以下这些最新应,包括: 带智能包处理和流量管理功能的400G OTN;带智能波束形成功能的4X4混合模式LTE和WCDMA无线电;带智能图像增强与识别功能的4K2K和8K显示屏 ;用于智能监视与侦查(ISR)的最高性能系统 ;数据中心使用的高性能计算应用等。

作者: 孙昌旭 来源:电子工程专辑

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网