作者:Steve Leibson, 赛灵思战略营销与业务规划总监

2014光纤通信大会在美国旧金山Moscone中心盛大开幕。华为公司和赛灵思公司利用这次会议联手发布400G路由器原型。由于400GE标准现在仍未完成制订,因此这款400G原型路由器仍待改善,不过它为运营商提供了一个展示平台,这些运营商已经预见到未来数年数据海啸将要袭来,因为将有500亿台智能设备或3000亿无源 “物”会连接到互联网。根据2012年IEEE 802.3 BWA (带宽评估)报告,核心网络流量每18个月翻一番,而服务器输入输出带宽则每24个月翻一番,因此在100G标准完成后需尽快完成400G以太网标准。

其实400GE标准制定工作已经开始,但主要的网络设备供应商如华为等不及标准落地就必须开始加紧硬件开发。故此华为开发团队选择使用可编程逻辑器件,开发400G线卡、总线架构和背板,它们要支持华为NetEngine NE5000E 集群路由器的高吞吐量线卡。

这款产品的联合发布人华为重要标准策略师(Distinguished Standards Strategist)Chuck Adams指出,这款400G原型系统的开发,显示华为已能支持新兴的400GE标准,这个原型系统也证实了华为系统的可行性-----不管64字节的包还是1518字节的数据包,都没有出现丢包现象,这也证明了华为所选择的方法和器件技术可以支持400GE系统的带宽和功率需求,同时给华为实现了领先2年的系统开发时间----华为可以有充足的时间应对标准完善引发的系统设计修正。

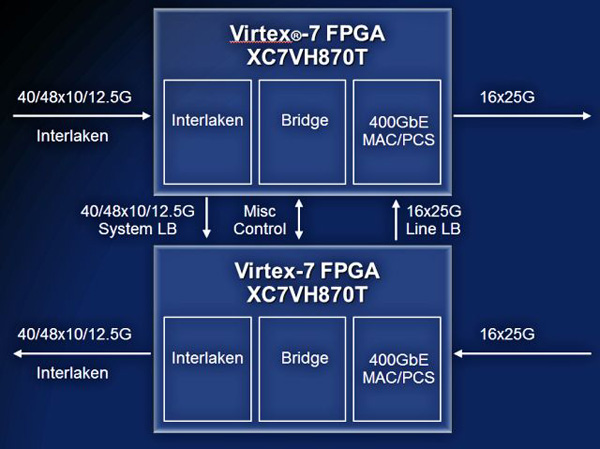

以下为华为原型400G原型线卡架构框图:

这个400G线卡包括两个主要的子系统:400G发送端和400G接收端。发送端和接收端集成了16 个25G端口以创建400G发送和接收通道。两个子系统采用Interlaken协议与NetEngine路由器的背板通信。

这两个子系统均在Xilinx Virtex-7 XC7VH870T Heterogeneous 3D FPGA实现,该系统集成16个28Gbps低抖动GTZ SerDes收发器和72 个13.1Gbps GTH串行解串收发器。这个系统运行频率312.5MHz,以1280-bit宽总线实现了400G吞吐量。华为工程师们之所以选择这些特殊的All Programmable器件是因为,他们采用的半导体器件需要在有限的功率预算内完成与 四个CFP2光模块和Interlaken背板的高密度连接。

下图是设计完成的400G线卡LPUF-480A的图片,线卡面板上的四个矩形接口支持100G CFP2光模块。除了两个赛灵思 Virtex-7 XC7VH870T异构3D FPGA而外,LPUF-480A线卡采用多种类型的高速存储器,包括DDR3 SDRAM、QDR SRAM和RLDRAM, FPGA中的各种存储器接口控制这些存储器。

值得一提的是这款原型系统基于赛灵思28nm Virtex-7 3D IC。该设计布局周密可以方便地移植到赛灵思下一代基于UltraScale架构的20nm单芯片FPGA。这些器件的逻辑密度更高、功耗更低,还可以实现更高性能。

原文链接:

http://forums.xilinx.com/t5/Xcell-Daily-Blog/Huawei-and-Xilinx-unveil-pr...

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网