作者:Steve Leibson, 赛灵思战略营销与业务规划总监

了解Zynq PS / PL接口之后;到目前为止,我们已经分析了Zynq All Programmable SoC芯片中的PS (处理器系统)与PL(可编程逻辑)之间的接口。我们已经使用Vivado设计套件创建了简单的外设,使用SDK与新外设连接,并且可以在外设上运行自检程序。但我们创建的外设功能不超过四个可读取和写入的寄存器。实际上,我们需要外设执行一些有效的功能。

我们将再次使用Vivado为这个外设添加实际的功能。

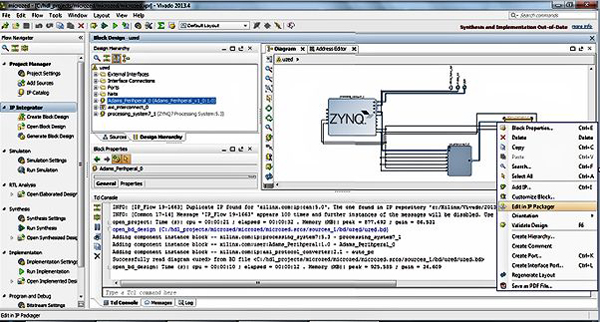

首先需要打开Vivado项目和框图,其中包含我们已创建的外设。右键点击“Peripheral”,选择“Edit IP Packager ”选项。随后IP Packager窗口将打开,可编辑和更新外设。

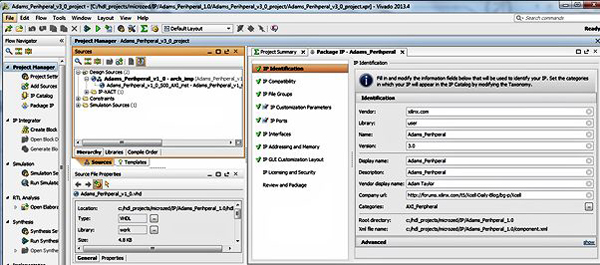

除Package IP 外设窗口外,这个窗口与标准项目流窗口相似。在设计源窗口下方有两个在外设创建过程中创建的文件。

这些文件被命名为:

Adams_Peripheral_v1_0.vhd - 顶级架构文件,利用该文件可定义退出该模块的用户I/O。

Adams_Peripheral_V1_0_S00_AXI.vhd - RTL文件,其中包含函数AXI接口,包括初始创建的四个寄存器。

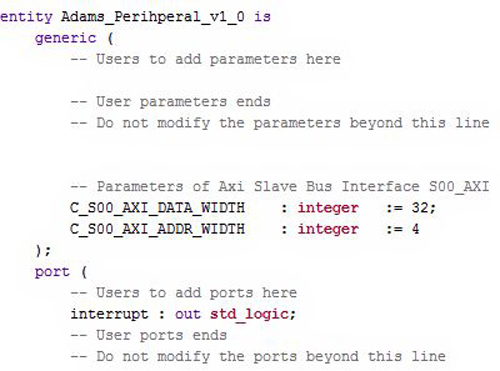

这两个文件中包括用户代码将插入地址的注解:

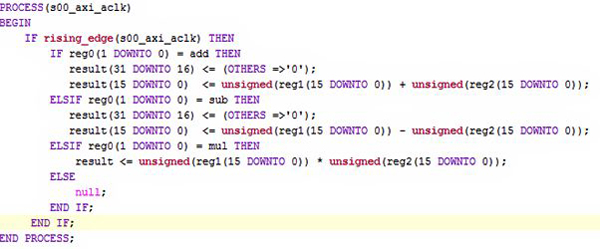

在这个例子中,我将介绍使用第一个寄存器作为控制寄存器。这个寄存器当中的特定位定义是否将寄存器2和3的目录进行相加、相减或相乘运算。运算结果将存储在第四个寄存器中。我们将设置与微处理器相关的第四个寄存器为只读状态,以确保微处理器不会影响运算结果。此外,如果激活控制寄存器,外围将生成一个中断。

定义中的第一步是声明四个寄存器,第3个寄存器为输出寄存器,最后1个寄存器为输入寄存器。(在这个步骤时我们可实现这一功能,但目前我正在顶层操作演示实现更复杂功能所需要的步骤) 。

同时,我也编辑这个文件为只读文件,以防止处理器写入第四个寄存器。

在顶层文件我在该架构创建一个中断输出并添加简单功能代码以执行我们所要的操作。

在所有必要的用户VHDL语言完成添加后,我处理该项目以确保在Vivado内打包IP并返回至项目前不会出现错误。但在打包器打包IP前,我增加IP版本号以表示代码变更。点击“re-package”将运行打包器,并关闭项目,返回至初始Vivado项目。

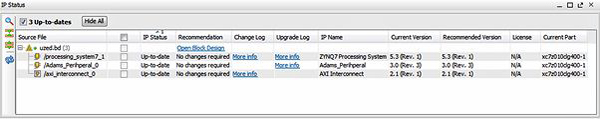

返回使用该外设的项目中,可以运行IP状态报告(Tools - >Reports - >Report IP status),显示在设计中所使用的更新版本。

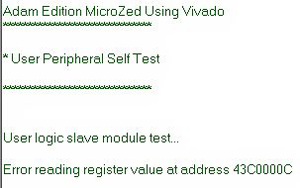

在将项目导出至SDK前,需要重新构建项目。在SDK内,可使用之前使用的同一功能对这个外设进行写入和读取。但测试过程中最后一个寄存器不能写入时,自检程序将失败。

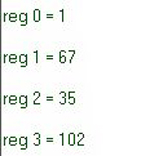

第一个测试是使用寄存器0中的命令1相加寄存器2和3内的目录:

在第二次测试中,我们使用寄存器0中的命令2将寄存器2和3内的目录相乘:

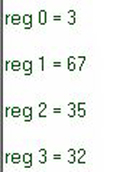

在最后的测试中,我们使用寄存器0中的命令3将寄存器2内的目录减去寄存器3的目录:

所有这些测试都使用轮询的方法。由于这些运算属于简单的加、减、乘函数,可在一个时钟周期内完成。但更复杂的多周期函数运算需要使用中断,我们将在另外的文章中说明。

请参阅由Adam Taylor编写的有MicroZed系列相关文章:

Zynq PS/PL第三篇 ——Adam Taylor 有关MicroZed之23

Adam Taylor玩转MicroZed连载22:详解Zynq 的PS/PL(第二部分)

Adam Taylor玩转MicroZed连载21:详解Zynq 的PS/PL(第一部分)

亚当泰勒玩转MicroZed连载20:Zynq三重定时器/计数器介绍之第四部分)

亚当泰勒玩转MicroZed连载19:Zynq三重定时器/计数器介绍之第三部分)

亚当泰勒玩转MicroZed连载18:Zynq三重定时器/计数器介绍之第二部分)

亚当泰勒玩转MicroZed连载17:Zynq三重定时器/计数器介绍之第一部分)

亚当泰勒玩转MicroZed连载16:Zynq SoC专用看门狗

亚当泰勒玩转MicroZed连载15:实现Zynq SoC专用定时器

亚当泰勒玩转MicroZed连载14:MicroZed定时器、时钟和看门狗

亚当泰勒玩转MicroZed连载13:再谈MicroZed中断

亚当泰勒玩转MicroZed连载11:使用MicroZed按键实现输入

亚当泰勒玩转MicroZed连载10:驱动Zynq SoC GPIO

亚当泰勒玩转MicroZed连载8: MicroZed XADC软件

亚当泰勒玩转MicroZed连载7: 让MicroZed跑起XADC

亚当泰勒玩转MicroZed连载6: MicroZed引导加载器

亚当泰勒玩转MicroZed连载4: 在MicroZed上跑你的程序

亚当泰勒玩转MicroZed连载3: 让Zynq和MicroZed说“hello world”

原文链接: http://forums.xilinx.com/t5/Xcell-Daily-Blog/The-Zynq-PS-PL-Part-Four-Ad...

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网