作者:Steve Leibson, 赛灵思战略营销与业务规划总监

现在, IBM已经推出了POWER8微处理器和 OpenPOWER基金会,赛灵思已经宣布成为该基金会成员,在拉斯维加斯举办的IBM Impact 2014大会上进行的演示,以及CAPI将会在Xcell每日博客上发表。什么是CAPI ?这是IBM POWER8处理器的“Coherence Attach Processor Interface”,在设计上用于在8个片上多线程微处理器内核POWER8芯片阵列无缝添加处理加速器。CAPI允许外部硬件加速器使用片上处理器使用的相同内存地址,并实现指针废弃。也就是说加速器将查看应用程序可查看的同样存储空间。(以下为Hot Chips 25所做的IBM POWER8 演示链接,对CAPI提供了相关信息。)

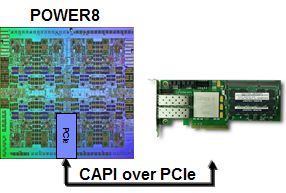

IBM POWER8处理器采用硬件管理缓存一致性,使得CAPI连接的加速器锁定同程线程运行所占用的内存,以与常规处理器加速器协议相比可提供的更低延迟与加速器连接。CAPI使用片PCIe Gen3 接口与外部硬件加速器连接。

本周举行的IBM IMPACT 2014会议所做的Xilinx 演示基于CAPI CAPI-based key value store负载加速引擎,可用于许多常见的数据中心应用,包括Memcached和NoSQL,以提供应用加速,同时提高性能/ W。Xilinx CAPI演示还使用了集成在Vivado HLS内的OpenCL的设计环境。

原文链接:

http://forums.xilinx.com/t5/Xcell-Daily-Blog/IBM-s-OpenPOWER-Foundation-...

© Copyright 2014 Xilinx Inc.

如需转载,请注明出处