作者:Steve Leibson, 赛灵思战略营销与业务规划总监

3D Plus Fusio-II封装使用3D堆在19x19x3.9mm封装中放置4个模块——一块赛灵思Spartan-6 XQ6SLX150T FPGA,两块移动DDR(mDDR)SDRAM和NOR FLASH器件——还有167旁路电容,过滤10个电源。该模块有比它采用的Spartan-6 FPGA更小的pcb印制板——361mm2比937mm2。这是封装器件的一张图:

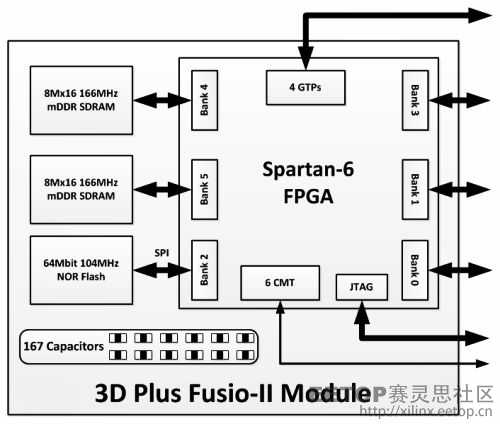

封装内连接数量也较少,因为一些FPGA的I/O bank用来连接模块上的内存模具。这里是一张模块的方块图:

该模块使用3D Plus’ WDoD(Wire-free Die on Die)技术,使用侧壁金属化来互联堆积的模具。根据3D Plus,WDoD方法不使用内插器。与丝焊技术相比,3D Plus’ WDoD互联电容更小,电感略大(见“Stacking of Known Good Rebuilt Wafers for High speed Memory and Systems in Package”.)。

Fusio-II模块目前有货,商用的温度范围为0-70°C,工业用的温度范围为-40°C/ +85°C

原文链接:

http://forums.xilinx.com/t5/Xcell-Daily-Blog/3D-Plus-module-puts-Spartan...

© Copyright 2014 Xilinx Inc.

如需转载,请注明出处