作者:Adam Taylor

我本来打算在这篇博客中继续介绍探讨运行于Zynq SoC上的操作系统。然而由于上周有人提问过一些关于Zynq SoC外设XADC,中断和alarms的问题,我认为我们应该快速的了解一下以及我们怎样将它们加入到系统设计中。

Zynq SoC具有检测供应电压和片上工作温度的能力,这看起来非常有趣 。我们可以利用这个功能在系统测试期间验证初始供应电压和工作温度。在我们的设计的整个测试和运行期间,我们可以定期的检查确保这些参数保持在规定的运行 范围内。在系统运行期间我们也可以用这个功能来判别Zynq SoC的运行环境是否存在问题,可能导致系统启动运行失败的问题,例如:缓慢漂移的电压和电流。

Zynq SoC具有很多可屏蔽的中断,可以中断两个片上的ARM Cortex-A9 MPCore

Processors,通过产生一个在用户定的的最大参数设置和最小参数设置范围外的一个警报参数。XADC拥有它专用的中断,由两个处理器内核共享,中

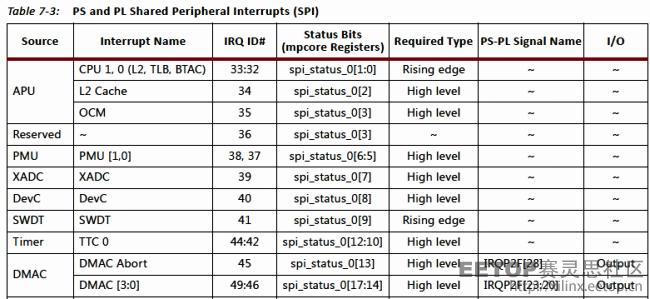

断号为IRQ39,正如下面的从Zynq TRM(技术参考手册)中截取的图表所示:

在使用Vivado软件配置XADC的时候我们可以设置一些警报参数,如下面所示:

这些参数也可以在软件环境中调用xadc_ps.h函数时进行设置,例如:

XAdcPs_SetAlarmThreshold(XADCInstPtr, XADCPS_ATR_TEMP_LOWER,(TempRawData));

XADC提供了很多警报输出信号,这些信号可以连接到在Zynq SoC PL(可编程逻辑)侧实现的逻辑模块上。这些逻辑模块可以启动警报操作,它们也可以驱动外部的一些指示器,

例如LEDS,位于开发板的前面来显示设备的运行状态。这对提供可视化的温度警告是非常有用的,例如系统风扇启动失败等等。

这些警报信号(总共7个,如上面图表所示)可以通过调用合适参数的函数进行使能,例如由xadcps_hw.h文件提供的调用函数。如果需要更多的警报信号,可以通过或操作(OR)将他们集中在一起调用。

一旦我们使能了警报函数,我们也可以使用合适的调用函数使能中断,同样使用xadcps_hw.h文件提供的函数。如果想一次使能更多的中断操作,同样可以使用或(OR)操作。

考虑到这一点,我在Vivado软件中创建了一个简单的工程,将Zynq PS 通过AXI接口连接到XADC,例如我不会使用任何的外部模拟量输入,但是使用器件内部的温度测量功能,即Zynq XADC。

使用软件配置XADC来中断处理器内核,比如出现高于或低于器件启动时的温度,增加或减少几度。现实中可能我们不需要如此严格的要求系统运行温度。然而这是一个展示XADC中断的应用,在Zynq SoC正常运行期间系统温度的变化将处罚中断操作。

我已经在这篇博客中附加了程序代码,主要分为三部分功能:

1. 第一部分是配置Zynq SoC的通用中断控制器,因此我们可以使用XADC中断作为这个中断服务例程的一部分,当声明XADC中断时调用。

2. 第二部分是配置XADC,设置定时计数器为安全模式,在读取温度前屏蔽所有警报函数。根据刚刚读取的温度设置温度警报范围的上限和下限温度值。设置好这些参数值后,就可以设置温度警报函数和使能温度中断操作。

3.第三部分是当温度中断操作发生时,中断服务程序将被调用。这个例程将会清除中断状态寄存器,屏蔽其他所有的中断发生,当中断发生时读取温度值。读取的 温度可能不会高于中断温度,因为这个温度值将会不断的波动,我们不会计算温度的平均值,然而这个值会非常接近警报温度。

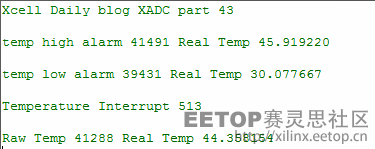

当我编译这个例程的代码并生成启动镜像 ,下载到MicroZed开发板上运行几分钟后,我观察到的结果信息如下:

正如你所看到的,中断被触发了,数字“513”(十进制)是随着XADC中断状态寄存器中的值不断更新的。

对于系统和FPGA设计者来说,XADC是一个非常有用的工具。这个简单的例子展示了我们怎样使用它作为系统运行状态的预兆。在一个更重要关键的程序中,我们可以使用它作为反篡改程序的一部分。

原文链接:

http://forums.xilinx.com/t5/Xcell-Daily-Blog/Adam-Taylor-s-MicroZed-Chro...

© Copyright 2014 Xilinx Inc.

如需转载,请注明出处

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网