作者:Steve Leibson, 赛灵思战略营销与业务规划总监

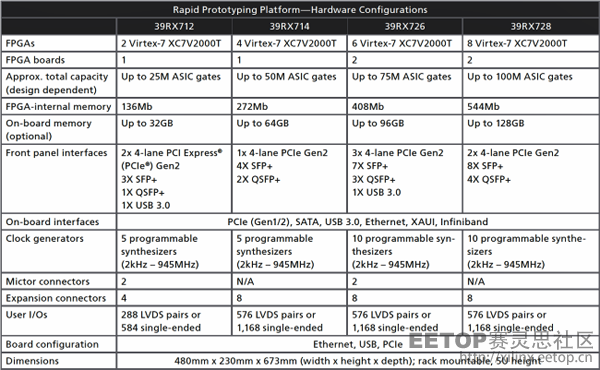

当你在设计SoC时,你需要找到设计中的bug,目前从A点到B点快速甚至是最快的的方法就是FPGA仿真,这与基于软件的仿真器相比能够运行真正SoC固件的FPGA仿真要快得多。这就是你需要为软件开发、硬件验证、硬件/软件集成和复杂SoC的回归测试所做的。Cadence刚介绍了它们的第二代基于FPGA的Protium快速原型平台。Cadence的Protium快速原型平台基于Xilinx Virtex-7 2000T 3D FPGA。(见“Generation-jumping 2.5D Xilinx Virtex-7 2000T FPGA delivers 1,954,560 logic cells, consumes only 20W”)一共有4个版本的平台,分别有2、4、6、8块Virtex-7 2000T 3D FPGA。这里有一张来自Protium数据册的四种快速原型系统的对比表:

与Cadnece第一代快速原型平台(RPP)相比,Protium提供了其4倍逻辑门数量和3倍内存。因此,你可以用这个快速原型平台开发更大的项目。Cadence也为这个第二代Protium平台提供了来自它的兄弟——Cadence的 Palladium XP验证计算平台的设计流程。该公司声称, 这就导致加速了5倍的编译时间。

就像Cadence的Richard Goering在他的Industry Insights博客中写到:

“基于FPGA制作原型面临最大的困难就是启动时间——就是所有时间,包括编译ASIC设计,写入多块摆放完、路由完也验证完的FPGA,并且完全实现了系统功能。‘很快地做出一个原型是非常重要的,因为每周都离你真正能够使用近一点’, Cadence高级产品经理Juergen Jaeger说,‘我们的目标就是吧开发FPGA原型的时间从几个月缩短到几周。’”

根据Goering的博客,Protium平台提供了3种性能模式:

• 全自动模式,自动化的ASIC内存映射,分区和以5-10MHz运行的FPGA放置与路由

• 手动引导模式,从设计团队里获得SoC分区信息,以20-50MHz运行

• 黑箱模式,将SoC设计放入一块Xilinx Virtex-7 2000T 3D FPGA,以高于100MHz运行

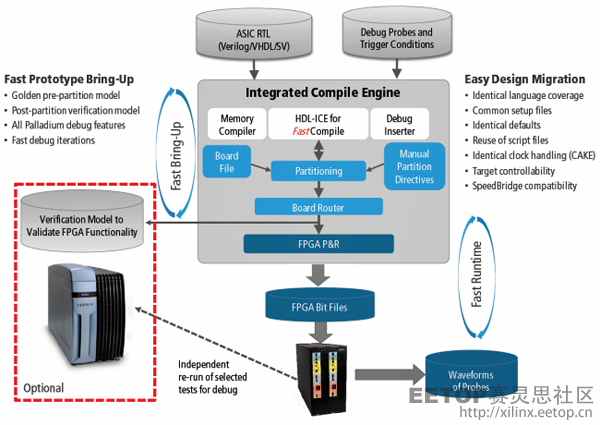

这里有一张使用Protium仿真平台的设计流程的图表:

如图所示,Palladium设计现在前后为Palladium(左边虚框)和Protium(底部)服务。这个统一化的设计流程能够把这两个工具比以前更紧密地结合在一起。

原文链接:

http://forums.xilinx.com/t5/Xcell-Daily-Blog/Cadence-announces-2nd-gener...

© Copyright 2014 Xilinx Inc.

如需转载,请注明出处

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网