昨天讨论了使用FPGA的一些引脚调试I2C串行协议,并介绍了在基于FPGA的设计中使用赛灵思PicoBlaze微控制器。(查看“仅使用两个I/O引脚,I2C通信协议和一个数字示波器调试你的FPGA设计”)PicoBlaze微控制器是众多的隐藏的可以应用与赛灵思公司产品结构中的宝贵资源之一。

• 占用最小型的Virtex-7 系FPGA的0.03%的资源(91050 slices)

• 占用最小型的Kintex-7 系FPGA的0.25%的资源(10250 slices)

• 占用最小型的Artix-7 系FPGA的0.3%的资源(5200 slices)

• 占用最小型的Spartan-6 系FPGA的4.3%的资源(600 slices)

换句话说,你可以轻松的在你的FPGA设计中实现不止一个PicoBlaze 处理器核,而且不用担心你所使用的FPGA系列的型号。

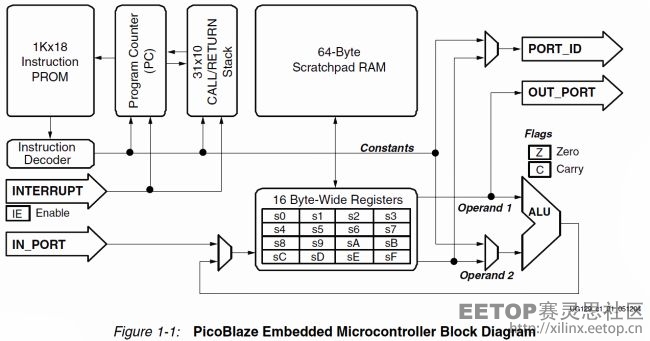

下面的是引用PicoBlaze用户指导手册的PicoBlaze微控制器的模块图:

那你为什么想要我使用一个(或多个)这样的PicoBlaze微控制器?而不是让我搭建扩展这个有用的工具呢?下面是一些使用过PicoBlaze微控制器的用户的一些反馈和评价:

“在我的赛灵思百宝袋里,我最喜欢的就是PicoBlaze处理器了,如果不是广泛使用了PicoBlaze处理器我就不能及时的完成我的工程项目。这个 设计包含了超过1000个这样的嵌入式处理器,分为九个不同的设计模块。PicoBlaze处理器通过时序复用逻辑电路提供高效的可利用的逻辑资源。 PicoBlaze处理器同样也提供了简便快捷的方式来开发一些控制功能。最好的选择可能是为每个功能函数设计定制一个状态机。实际上PicoBlae处 理器就是一个可编程状态机,也就是在处理器核中已经建立了状态机,我们需要做的就是对它进行编程,实现状态控制。”

“PicoBlaze让我们众所周知的FPGA开发环境转变为一种基于软件应用的开发方式,这种转变是无缝的,是非常简单的。”

“我可以把PicoBlaze作为一个模块,引入到我的设计中,以绝对最少的接口连接问题实现执行顺序的任务。事实上,我是一名物理学家,但是我发现是用这样的众多处理器组合实现复杂高速的信号处理系统的开发是非常的轻松和简单的。”

“通过适应汇编语言,仅使用一个单通道Block RAM就可以实现大量数据的操作,这个小型PicoBlaze处理器让你有更多的空间资源实现其他的逻辑功能,所以引入更多的PicoBlaze就会有更多的空间逻辑资源。”

Ken Chapman是一名任职于赛灵思的首席工程师,自从1993年就开始关心并且维护升级赛灵思 PicoBlaze微控制器了,应经有20多年了,下面是Ken对于PicoBlaze微控制器所作的介绍和评价:

“PicoBlaze是运行情况是高度可预测的,在任何情况下每条指令的执行都会耗时两个时钟周期,这样就可以满足时序的要求;当需要实现时序要求时,I2C和SPI协议可以轻松的满足要求,但是UART串行传输需要相当的准确,因为没有一个参考时钟。”

我想说的是,就实现一个硬件的状态机而言,使用PicoBlaze来实现更加的简单容易。对于设计硬件(Verilog或VHDL实现)方面做的任何修改 都需要对整个设计重新编译(包括综合,布局布线,生成bit流文件和重新配置硬件),相反的,PicoBlaze程序存储在BRAM(通常1K的指令就足 够多了,只需要一个18kbit的块内存)中,可以通过JTAG Loader进行动态修改,JTAG Loader在PicoBlaze的封装库中有提供。

你可以改变你的bit-banging程序的一行代码,并且让它在硅逻辑电路中以少于15秒的时间完成运行。这样实现了一种互动模式的开发方式。例 如,你能够在示波器上观察各种信号量,并且可以看到信号量会根据你的代码实时的改变。实际上,这些信号量很容易获得,具有挑战的部分是实现正确的传输协 议,如果使用硬件状态机就会比较复杂。

如果PicoBlaze不在你的赛灵思“工具箱”中,也许现在是时候添加进去了。点击这里下载包含所有信息的ZIP格式的文件。

原文链接:

http://forums.xilinx.com/t5/Xcell-Daily-Blog/Hidden-Gems-The-Xilinx-Pico...

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网