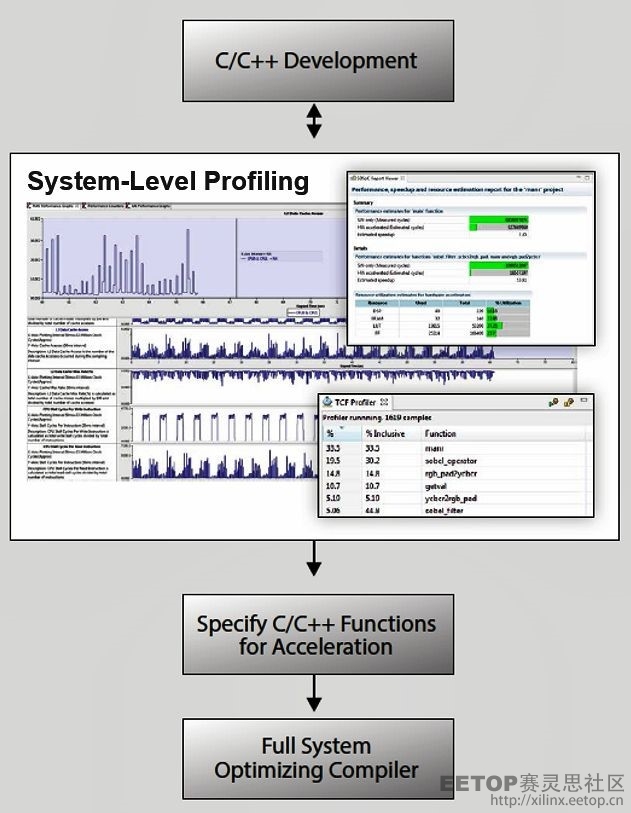

SDSoC的工作流程如下:

整个流程很像纯软件的嵌入式设计,但是它更快,这得益于可编程逻辑上的硬件加速器。

SDSoC开发环境利用片上逻辑资源创建软件可用的硬件加速器,该片上资源是基于程序编译指示,编程分析,计划,硬件连接模式的连接。SDSoC使用特定的板级支持包(BSP)来创建:

然后全系统优化的编译器自动将系统编译为一个完整的软件或者硬件系统。同时也会生成可编程逻辑比特流文件和用于ARM的ELF文件。

在此,尽管你没有在上述流程上看到Verilog 或VHDL,这并不意味着赛灵思砍掉对HDL语言的支持。SDSoC开发环境会封装和自动生成HDL、综合、布局布线就像C/C++编译器封装和自动完成代码优化和转化为目标语言一样。

SDSoC开发环境包含许多基于Zynq的开发板的支持包,包括ZC702,ZC706,赛灵思图像处理开发板,以及第三方的安富利的 Zedboard,Microzed和德致伦的ZYBO开发板。这些支持包(BSP)包含元数据使得SDSoC开发环境可以抽象化嵌入式平台以提高生产效 率和加速研发周期。

这里演示一个7分钟例子来展示通过一个简单的方法能够在视频Pipeline系统上提升60x速度的代码执行过程。

SDSoC开发环境系统优化编译器使用ARM和可编程逻辑在最短的时间内来实现系统任务。SDSoC使得系统架构师和软件团队使用“万能的”C/C++来 快速地实现片上资源的优化,自动生成系统连接以提高系统内部连接性能。嵌入式系统设计师可以权衡性能,数据吞吐量,延迟,同时缩短设计周期。

这可能不是你第一次碰到嵌入式自动化工具了,所以,你可能对此还是持有怀疑态度。但是,你必须知道SDSoC系统编译器是基于赛灵思高层次综合(HLS)编译技术的,且这项技术已经有超过1000个开发人员使用。就是说,已经有许多人在你之前使用了SDSoC开发环境了。

SDSoC是SDx开发环境系列的第三款产品,这些产品带来了显著的性能提升和功耗降低,应用于广泛的系统开发人员和软件工程师,例如高速网络 (SDNet),数据中心应用(SDAccel),现在是嵌入式系统(SDSoC)。SDx开发环境提供非常简单,类似于ASSP的开发流程,使你可以不 用变成HDL专家也可以在可编程逻辑获得性能上的提升。

SDSoC已经发布了前期版本。如果这个新工具适合你的团队,请联系赛灵思及我们的授权分销商销售。他们会为你更加详细的介绍。