k2与k1一样,唯一不同的是:k2是在clk的下降沿变化。最后将k2与k1进行或运算即可得到占空比50%的任意奇数分频器。

4.半整数分频器

半整数分频器原理如图3所示[3].主要包括模M计数器,异或模块和2分频模块三个部分。其设计思想是:通过异或门和2分频模块组成一个改变输入频率的脉冲添加电路,即在M-0.5个输入信号周期内产生M个计数脉冲,并将其中的一个计数脉冲的周期变为含有两个脉冲的周期。而这种改变的具体实现是将原始时钟信号与2分频模块的输出进行异或。

另外,不难发现此原理图还可以实现占空比为50%的2M-1倍的奇数分频。当M=3时,其仿真结果如图4所示。原理图的输出端口q即为占空比为50%的5分频,输出端口C为2.5分频。

5.数控通用分频器的实现

综上,利用模N计数器、脉冲添加电路,以及控制模块即可实现占空比可调的通用分频器。在具体设计过程中可采用层次化的设计方法。首先,设计通用分频器中各组成电路元件,然后通过元件例化的方法,调用各元件,实现通用分频器。

其中:

模N计数器的实现可以采用两种方式:

一是调用L P M库中的参数化的计数器模块LPM_COUNTER,根据向导对参数进行设置,QuartusII会生成相应的。vdh计数文本。为了能够调用计数文本,最后还需要利用VHDL语言对该计数文本设计一个例化程序,并将其设置为顶层文件。二是利用VHDL描述语言实现。

二分模块是利用D触发器来实现的,即将D触发器的输出信号Q反馈回来作为输入信号,将模N计数器输出信号的最高位作为D触发器的时钟信号。

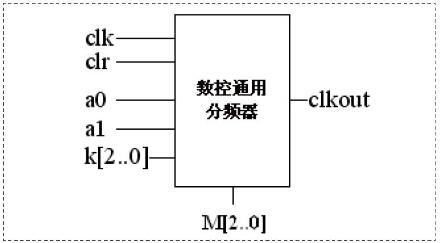

其顶层原理图如图5所示。其中a为分频模式选择,当a=00时进行偶数分频;当a=01时进行占空比为非50%奇数分频;当a=10时进行占空比为50%的奇数分屏;当a=11时进行半整数分频[2].端口M的作用是控制分频数。端口K的作用是进行偶数(M=2N)和奇数(M=2N+1)分频时,调节占空比,当k=N时,占空比为50%.

6.结论

本设计的最终目的是实现分频器的通用性和实用性,本设计中控制端口M、K、以及计数器N的位宽均采用参数化设计思想,用户根据需要对其稍加修改就可满足不同的分频需求,在一定程度上实现了通用性。