作者:杨晓安1,罗 杰2,包文博2 (1.珠海广播电视大学信息工程系,广东珠海519000;2.华中科技大学电子与信息工程系,湖北武汉 430074)

摘 要:为了对障碍物距离精确测量,基于最新Zedboard FPGA(现场可编程逻辑阵列)开发板,采用软硬件协同的设计 方法,设计了障碍物距离测量系统的软硬件。系统为智能小车平台提供了完整的距离测量服务,测距范围能够达到2cm~4.5m,精度可达0.2cm。该设计包含从底层硬件电路设计、可编程逻辑IP(IntellectualProperty)核设计、到Linux设备驱动的设计全部流程,对于在Zynq⁃7000FPGA上软硬件从事开发的人员有一定的参考价值。

随着集成电路的制造和应用技术的快速发展,嵌入式系统的性能也不断提升,已经被广泛应用于工业控制、航空航天、军事以及消费电子等领域。在硅工艺的发展以及市场推动下,Xilinx公司推出了基于7系列FPGA的新一代全可编程(AllProgrammable)Zynq⁃7000系列产品。该系列产品,集成了嵌入式领域集大成者——双核ARM CortexA9处理器和7系列28nm工艺FPGA芯片。Zedboard正是这样一款基于Zynq⁃7000产品的实验 开发板卡,提供了软件和硬件设计的更多可能。本文基于目前FPGA业界最先进的Zedboard FPGA(现场可编程逻辑阵列)开发板,从底层硬件电路设计、可编程逻辑IP(IntellectualProperty)核设计、到Linux设备驱动的设计,实现了障碍物距离测量的软硬件系统,并在智能小车平台上,实现了距离测量服务。该方法对于在Zynq⁃7000FPGA上软硬件的开发具有指导作用。

1、系统设计

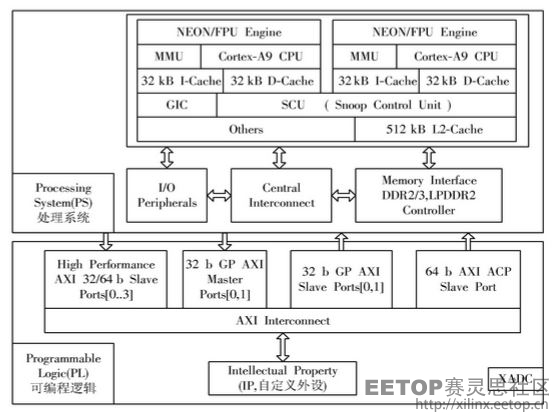

传统上,FPGA中嵌入处理器内核,都是以FPGA为 主、处理器为辅,设计思路以可编程逻辑为主。然而新一代全可编程的Zynq⁃7000采取不同的思路,它是以处理器为主,FPGA为辅。FPGA变成了ARM处理器的一个协处理器[1]。图1为Zynq⁃7000SoC芯片的结构图。 简单来说,Zynq由PS和PL两部分组成:PS(Pro⁃cessingSystem,处理系统)相当于一片ARM芯片,而PL (ProgrammableLogic,可编程逻辑)相当于一片FPGA芯片。

图1:Zynq结构图

PS系统结构为:双核A9处理器,其是整个平台的控制中心,处理速度高达1GHz,可通过NEON扩展及单精度浮点单元进行增强,拥有32KB指令及数据L1 缓存,统一的512KBL2缓存和256KB片上存储器;存储接口,用以管理片内系统的存储状态,包含DDR3,DDR2和LPDDR2动态存储控制器和两个QSPI,NANDFLASH及NORFLASH控制器;通用外设,PS中的通用外设是ARM直接和外部设备通信的接口,含SPI,I2C, CAN,UART,GPIO,USB2.0等;其他组成部分。

PL部分结构为:低功耗可编程逻辑,包含28K~ 350K个逻辑单元,240K~2180K可扩展式BlockRAM和80~900个DSPSlice;XADC,为PL内置的12b模/数转换器;通用/定制外设,PL中的外设是PL中的器件和 外部通信的接口。在ARM接口不够用时,可以利用PL的外设接口。PS和PL之间的数据交互,则是通过AXI(AdvancedeXtensibleInterface)接口实现的。具体有:高性能AXI接口(HighPerformanceAXISlavePorts),共4个;通用AXI接口,包括两个主设备接口和两个从设备接口,共4个;加速一致性端口,是ARM多核架构下定义的一种接口。

根据Zynq结构特点,在应用系统结构设计时注意,使用由Zynq这样一款功能强大的SoC芯片,与一般的ARM芯片不同,与常用的FPGA,更存在区别。它要求 硬件和软件之间进行协同设计,共同实现既定的性能指标要求。在SoC设计中,IP(IntellectualProperty,知识产权)核重用技术是一个很重要的概念,它是软硬件协同设计的关键,通过标准化IP核可以实现模块复用,可以完成大规模的、复杂的SoC设计[3]。

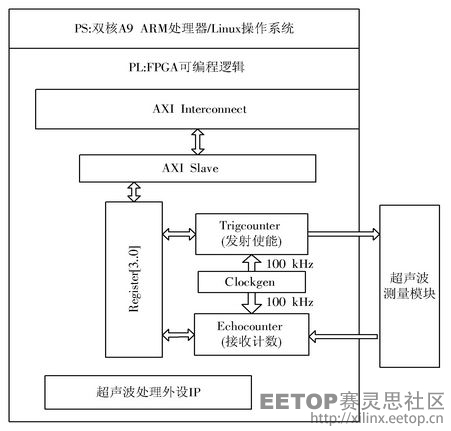

本文以一个超声波测距系统为例,介绍如何在ZynqSoC上,定制IP、设计Linux设备驱动等,并完整的阐述了从硬件到软件的设计流程。设计的系统结构如图2所示。PS上,运行Linux操作系统,为LinaroUbuntu发行版。根据文献[2]的指导操作,使用Xilinx公司的开发软件完成配置,使PS可以运行操作系统。

图2:系统结构图

PL部分按照系统控制的需求进行定制。设计基于 XilinxAXI总线的超声波处理外设IP核,与外部的超声波发射和接收电路交互。在Linux操作系统下,这个IP核就成为了一个设备,这就需要编写相应的设备驱动程序,实现超声波测距功能的封装。

2、 主要模块设计

2.1 超声波测距模块

该模块基本工作原理是:通过超声波发射探头,发射频率为40kHz的超声波信号;当超声波信号遇到障碍物时,会发生反射;当超声波接收探头接收到40kHz频率附近的声波信号时,经过信号调理电路;再通过系统计算接收与发射之间的时间差计算障碍物距离。

图3测距模块

设计中共使用到了三个相同测距模块,分别测量三个不同的方向上障碍物距离。测距模块分为超声波发射部分和接收部分,模块的电路结构如图4所示。具体是采用HC⁃SR04超声波测距模块,进行硬件设计[6]。该电路的对外接口为触发(TRIG)控制端和回响(ECHO)信号接收端。通过I/O口TRIG触发测距,提供了一个10ms以上的高电平触发信号,该模块将发出8个40kHz的方波用于探测,并自动检测是否有回波信号。一旦检测到有回波信号则通过I/O口ECHO输出一个高电平回响信号,且回响信号的高电平时间tH(单位:ms)即高电平持续的时间与所测的距离S成正比。其对应关系为:

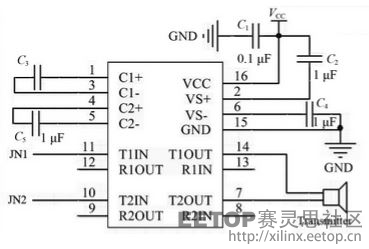

发射部分:利用串口转换芯片的升压功能,采用MAX232将输入JN1和JN2的3.3VTTL电平转换,得到5V电平。它激励超声波发射探头的信号压差为10V, 发出40kHz的超声波。如图4所示。

图4 发射电路

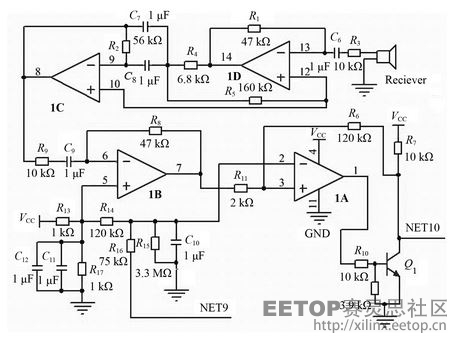

接收部分:对回波信号进行滤波、放大处理。接收电路图如图5所示。其中NET9为控制接收电路工作的使能端口,NET10为接收电路工作且接收到了回波信号时的响应信号。

图5: 接收电路图

2.2 IP核设计

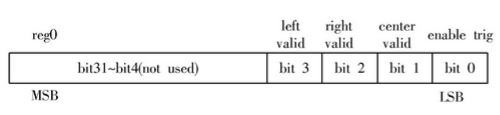

使用Xilinx的设计工具XPS(XilinxPlatformStudio) 建立IP的流程,新建一个Ultrasonic(超声波)IP核模块。该IP核的模块结构如图2所示中的超声波处理外设部分,其中Triggercounter,Clockgen和Echocounter使用VerilogHDL实现。根据超声波测距模块的测距时序要求,设计触发和回响信号的逻辑,由Triggercounter和Echocounter实现。最终将测量到的数据放到AXI4定义的寄存器中,使处理器能从AXI总线上读取数据。本IP核有4个寄存器(reg0~reg3),与AXI4总线相连,用户可以通过这4个寄存器控制发射超声波,获取测量的距离。其中,reg0的功能是使能一次测距以及三个方向上测量完毕标志,图6为reg0寄存器映射表;reg1~reg3为计数后计算得到的三个方向上超声波测量到的距离数值。将设计的IP核添加到XPS工程中去,分配得到的地址空间为0x6E000000~0x6E00FFFF。

图6:reg0寄存器映射表

2.3 Linux驱动设计

Linux设备驱动分为三类:字符设备、块设备和网络 设备。在这里需要编写的是一个字符设备[5]。另外,编写的设备将通过模块化的方式加载到操作系统中,而不是静态编译到内核中。驱动程序在交叉编译环境下,进 行模块化编译。得到以.ko为扩展名的驱动文件,使用 insmod和rmmod进行加载或者卸载,同时也可以通过lsmod查看是否已被加载。

建立一个ultrasonic_driver.c文件,使用交叉编译环 境进行编译,得到对应的可加载文件ultrasonic_driver.ko。在ultrasonic_driver.c中声明设备名称和模块的物理地址,该物理地址对应于XPS中建立的嵌入式系统的地址。具体如下:

#defineDEVICE_NAME"ULTRASONIC_MOUDLE"#defineULTRASONIC_MOUDLE_PHY_ADDR0x6E000000

该设备驱动的主要函数有:设备初始化ultrason⁃ic_driver_module_init();三个方向上的距离测量函数,sys_ultrasonic_front_get(),sys_ultrasonic_right_get()和sys_ultrasonic_left_get();设备注销ultrasonic_driv⁃ er_module_exit()。

(1)设备初始化函数,完成注册信息,当进行ins⁃mod操作时,操作系统会自动调用初始化函数,完成各 项信息的注册。而设备注销操作,与它相反,不做赘述。该初始化函数中,需要完成如下工作[4]:内核注册设备驱动;创建ultrasonic_driver设备类;为ultrasonic_driver设备类创建一个ultrasonic_driver_device设备;为设备创建以下几个文件:dev_attr_ultrasonic_trigger,dev_attr_ultra⁃sonic_front,dev_attr_ultrasonic_right,dev_attr_ultrason⁃ic_left,分别对应三个方向上的距离数值;将模块的物理基地址映射到虚拟地址上;同时将其他几个寄存器地址计算得到虚拟地址;打印调试信息,表明完成初始化工作。

(2)距离测量函数,以前向(front)测距为例,另外两个方向(right,left)上类似。Linux中,sysfs是一种基于ram的文件系统,它提供了一种用于向用户空间展现内核空间里的对象、属性和链接。sysfs与kobject层次紧密相连,它将kobject层次关系表现出来,使得用户空间 可以看见这些层次关系。可以通过CAT和ECHO接口命令来读/写sysfs。使用函数宏DEVICE_ATTR创建接口如下:

staticDEVICE_ATTR(ultrasonic_front,S_IRUSR|S_IWUSR,NULL,sys_ultrasonic_front_get);

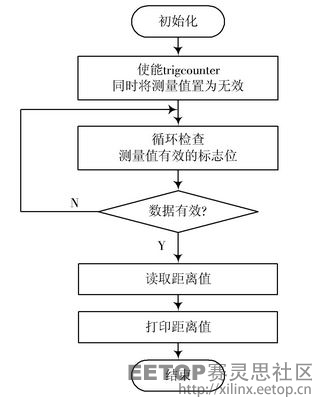

DEVICE_ATTR宏声明有4个参数,分别是名称、权 限位、读函数、写函数。其中读函数和写函数是读/写功能函数的函数名。这样对ultrasonic_front创建一个写函 数sys_ultrasonic_front_get,其流程图如图7所示。

图7:sys_ultrasonic_front_get流程图

进入函数,首先会打印一条调试信息;然后向reg0(ultrasonic_trigger_addr)上写入使能,使开始发射超声波;循环检测reg0的bit1,查看数据是否有效;如果数据有效,则读取出reg1(ultrasonic_front_addr)上的数据值,并打印出来。完成一次读取操作。 完成以上设备驱动设计后,使用配置好的交叉编译环境,将该驱动代码编译为ultrasonic_driver.ko文件。将该文件放入启动的SD卡中。

3系统测试

对XPS构建的系统,建立U⁃Boot引导,编译配置内 核源码,编译设备树,并制作根文件系统,制作ramdisk镜像文件,得到所有的文件zImage,devicetreee.dtb,ram⁃disk8M.img.gz,BOOT.BIN。放入Zedboard板的SD卡中,同时也将ultrasonic_driver.ko文件放入SD卡,上电启动,直至完成。

在连接到Zedboard串口的超级终端下,挂载SD,执行如下步骤:

mount/dev/mmcblk0p1/mnt //挂载SD卡

cd/mnt//进入SD卡目录

insmod./ultrasonic_driver.ko//加载ultrasonic_driver.ko模块

dmesg//查看加载打印信息lsmod//查看加载的模块

cd/sys/class/ultrasonic_driver/ultrasonic_driver

//进入创建的设备目录,sysfs下

catultrasonic_front//读取一次前向超声波测量距离

catultrasonic_right//读取一次右边超声波测量距离

catultrasonic_left//读取一次左边超声波测量距离

系统测试后可以在终端里看到打印的加载信息“ul⁃trasonicdriverinitialsuccessfully!”和读取到的测量距离数值。调整超声波探头前方障碍物距离,还可以得到不同的距离值,最终,实现的距离测量能够达到2cm~4.5m 的范围,精度可达0.2cm。

4结语

本文基于FPGA业界最先进的芯片Zynq以及开发平台Zedboard,融合软硬件设计,从底层的各功能电路设计,VerilogHDL代码编写,VerilogIP核设计,到Linux设备驱动设计,完成了整个设计流程,在智能小车平台上实现了在Linux系统中利用超声波测距的功能,达到2cm~ 4.5m的测距范围,精度达0.2cm,为上层应用提供了支撑服务。该系统设计对基于Zynq⁃7000FPGA上的开发的多个方面(例如,对ARM+FPGA应用设计的理解、软硬件结合的设计方法;Xilinx下AXI4⁃lite总线的IP核设计;Linux字符设备驱动设计)有指导性意义。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网