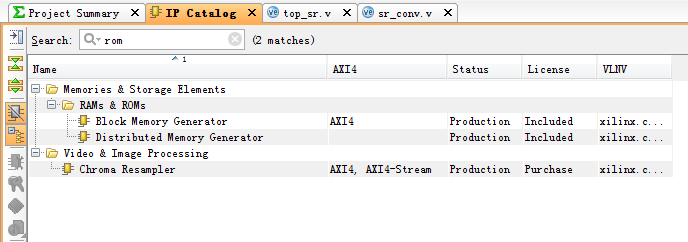

添加IP核

点击Flow Navigator中的IP Catalog,打开窗口添加IP核。

Block Memory为块存储设备,这里需要的是Distributed Memory Generator

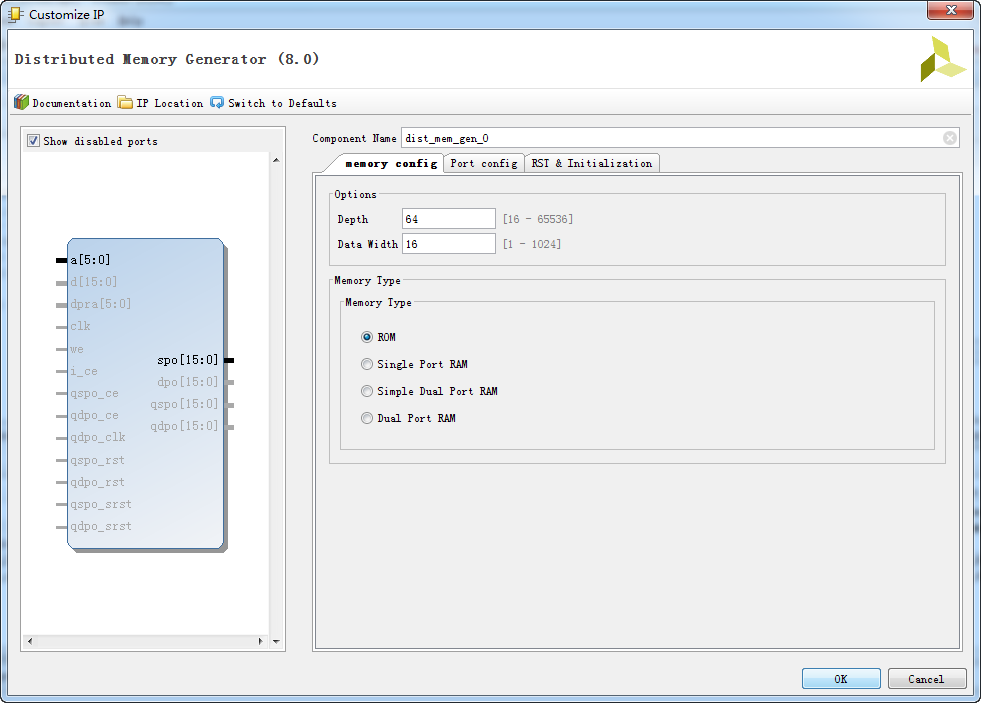

参数设置

设置参数:

- Component Name:生成的IP核模块名

- Depth:存储深度,即数据点数目

- DataWidth:数据位宽,即每个数据点的位数

- Memory Type:ROM,单口RAM,简化的双口RAM(一端读一端写),真双口RAM(两端都可读写)

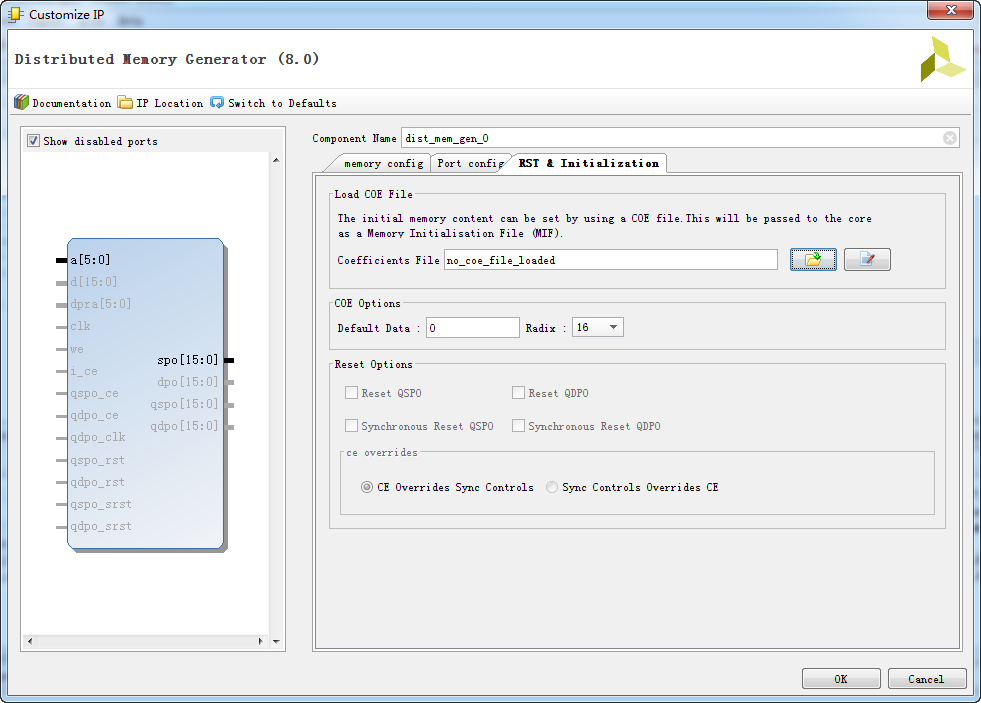

ROM的初始化

RST & Initialization:使用coe文件可以给ROM输入初值,格式如下:

MEMORY_INITIALIZATION_RADIX=2;MEMORY_INITIALIZATION_VECTOR=1000000000,1000001100,1000011001,1000100101,1000110010,1000111110,1001001011;

可以直接用文本编辑器写好COE文件(ISE和Vivado通用),第一个参数为进制,第二个为数据。COE文件最后会生成MIF文件用于初始化ROM。

调用方法

调用方法请参考

《Vivado的使用详细介绍:使用IP核》

http://xilinx.eetop.cn/viewnews-2468