第一期:MATLAB 和 Simulink协助 Zynq SoC 软硬件协同设计

发布者:jackzhang

时间:2015-12-16 21:01:02

作者:Eric Cigan 和 Noam Levine,MathWorks 公司 FPGA/SoC 技术市场营销部

2011 年赛灵思 Zynq®-7000 All Program-mable SoC 的推出为 FPGA 行业带来了突破性创新。这些器件通过将双核 ARM® CortexTM-A9MPCoreTM 处理器和丰富的可编程逻辑完美结合在一起,为大量应用提供了诸多优势。采用 Zynq SoC,设计人员既可享受在行业最常用的处理器上开发软件应用的好处,还能获得通过高速可编程逻辑架构上的硬件加速所提供的灵活性和吞吐量。

借助MathWo r k s ® 提供的 MATLAB® 和Simulink®,今天的创新者能够运用高度集成的软硬件工作流程创建高度优化的系统。本文提供的案例研究将讲述这一基于模型的工作流程。

赛灵思于 2011 年 12 月推出业界首款Zynq SoC时,设计人员就意识到他们可以将其传统的用分立处理器和 FPGA 构建的多芯片解决方案移植到单芯片平台上。他们可以在新平台上创建基于 FPGA 的加速器,扫除软件执行障碍,利用赛灵思及其 IP 合作伙伴提供的一系列的现成的生产就绪型 IP,满足数字信号处理、网络、通信等应用需求。

尚待解决的问题是他们如何为这款新器件编程。憧憬软硬件联合设计潜力的设计人员寻求的是能够在 ARM 处理器和可编程逻辑间对设计进行智能分区的集成工作流程。但他们找到的却是各自为阵的软硬件工作流程:一面是针对 ARM 内核的常规嵌入式软件开发流程;另一面是针对可编程逻辑的IP 组装、传统RTL 和新兴高层次综合工具组合在一起的硬件工作流程。

集成工作流程

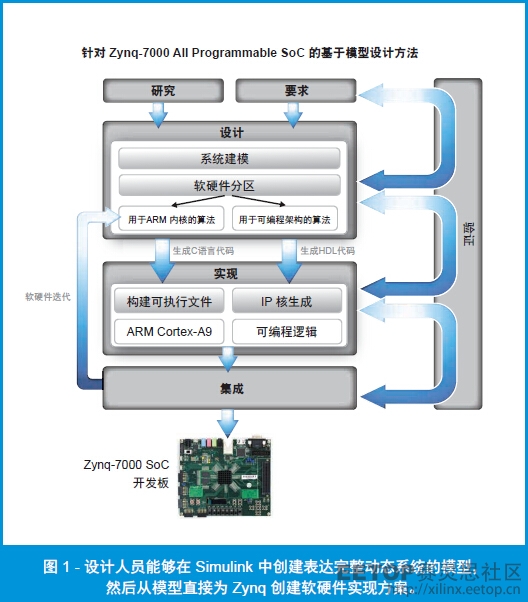

2013 年 9 月,MathWorks 使用基于模型的设计推出了一种 Zynq-7000 SoC 软硬件工作流程。在这个工作流程(图 1)中,设计人员可在 Simulink 中创建用于表达完整动态系统的模型(含用于针对 ZynqSoC 的算法的 Simulink 模型),还可直接从算法迅速创建针对 Zynq SoC 的软硬件设计。

系统设计人员和算法开发人员在 Simulink 中使用仿真为完整系统(通信、机电组件等)创建模型,以评估设计概念、进行高层权衡并将算法分配给软硬件。从 Simulink 生成 HDL 代码便于在 Zynq SoC架构上创建 IP 核和高速 I/O 处理。从 Simulink 生成C/C++ 代码便于为 Zynq SoC 的 Cortex-A9 内核编程,从而支持快速嵌入式软件迭代。

这种方法能够自动生成链接 ARM 处理系统和可编程逻辑的 AMBA® AXI4 接口,为 Zynq SoC 提供支持。通过与 C/C++ 编译、为 ARM 处理系统构建可执行文件、使用赛灵思设计工具生成比特流、下载到 Zynq 开发板等下游任务集成,实现了高速原型设计流程。

该工作流程的两大核心分别是:Embedded Coder® 和 HDL CoderTM 技术。Embedded Coder 负责从 MATLAB、Simulink 和 Stateflow 生成量产质量级的 C 和 C++ 代码,并对嵌入式系统进行针对性的优化。Embedded Coder 的应用已经相当广泛,当您驾驶现代乘用车、乘坐高速列车或搭乘商业航班时,这些交通工具极有可能就处于 Embedded Coder 实时生成的代码的控制之下。HDL Coder 与 Embedded Coder 对应,负责为 FPGA 和 ASIC 生成 VHDL 或 Verilog 并已紧密集成到赛灵思工作流程中。这种成熟的 C 和 HDL 代码生成技术是可编程 SoC 的基于模型的设计工作流程的基础。在通信、图像处理、智能电源和电机控制等领域中使用基于模型的设计的设计团队已经采用这一工作流程。

它是算法开发人员与硬件设计人员和嵌入式开发人员密切协作,加快算法在可编程 SoC 上实现的途径。当生成的 HDL 和 C 语言代码在硬件中完成原型设计,设计团队就可以使用赛灵思 Vivado® IP 集成器把该代码与其他生产所需的设计组件集成在一起。

案例研究:三相电机控制出于多种原因,具有高效电源转换能力的定制电机控制器是可编程 SoC 领域最常见的应用之一。更高性能、更高效率的方案是一个因素。在电机驱动系统占全球耗电总量 46% 的情况下,运用新颖控制算法实现更高效率是一个电机驱动设计追求的永无止境的共同目标。赛灵思 Zynq 可编程逻辑能实现精确的时序,是设计低时延高效率驱动器的理想平台。

另一个促进因素是多轴向控制。可编程 SoC 上丰富的可编程逻辑和 DSP 资源为在单个可编程 SoC 上实现多个电机控制器开辟了无限可能。不论电机是单独运行还是组合运行,都可受控于集成动作控制系统之下。

工业网络 IP 集成是又一大因素。赛灵思及其 IP 合作伙伴提供的 IP 用于与 EtherCAT、PROFINET 和其他能方便地集成到可编程 SoC 中的工业网络协议

集成。

为说明这一工作流程在通用电机控制案例上的运用,将以实现在 Zynq-7020 SoC 上的三相电机磁场定向控制算法为例(有关该硬件原型设计平台的详情,请访问:http://www.mathworks.com/zidk)。该电机控制系统模型包含两个主要的子系统(图 2):一个是针对已经在 Zynq 处理系统和可编程逻辑间完成分区的 Zynq SoC 的电机控制器;另一个是连接到配有测量轴角度的编码器的无刷直流电机的电机控制 FPGA 夹层卡 (FMC)。

可以从数据流的角度观察软硬件分区:

• 速度控制 (Velocity Control) 模块和模式选择 (Mode Select) 模块被分配给 ARM Cortex-A9 处理系统,因为这两个模块与模型的其余部分相比运行在较低速度下,也因为它们是设计在开发过程中最有可能修改和重新编译的部分。

• 运行在 ARM 内核上的模式选择 (Mode Select) 状态机负责判断电机控制器的运行模式(开环运行还是闭环调节)。该状态机负责管理在切换到闭环控制模式之前的启动、开环控制和编码器校准模式之间的切换工作。

• 编码器传感器信号通过外部端口传递给可编程逻辑中的编码器外设 (Encoder Peripheral),然后传递给位置/速度估算 (Position/Velocity Estimate) 模块,计算电机的状态(轴位置和速度)。

• 一个ΣΔADC 感知电机电流,随即由手动编码 ADC 外设模块处理该电流。• 电流控制器负责获取电机状态与电流、工作状态以及 ARM 内核通过 AXI4 接口传递的速度控制命令,据此计算电流控制器命令。在处于闭环模式下时,电流控制器使用比例积分 (PI) 控制原理,其增益可使用仿真和原型设计加以微调。

• 电流控制器命令穿越电压转换模块,通过 PWM 外设输出给电机控制 FMC,最终用于驱动电机。

设计人员能在 Simulink 中为完整系统建立模型(图 3)。

在基于模型的设计中,系统的顶层 Simulink 模型的组件数量增加到四个:

• 输入模型:负责向控制器提供受控轴速度和开/关命令,用作激励信号;

• 电机控制算法模型:主要用于 Zynq SoC;

• 设备模型:包括 FMC 驱动电子电路、无刷直流电机的永磁同步电机 (PMSM) 模型、电机轴上的惯性负载模型和编码器传感器模型;以及

• 输出验证模型:包含后处理和图形功能,有助于算法开发人员优化和验证模型。

在 Simulink 中可以在远早于开始硬件测试的时候就借助仿真彻底检验该算法。可以细调 PI 控制器的增益,尝试多种激励配置,检验不同处理速度的结果。在使用仿真的时候需要面对一个根本性问题:由于电机控制中一般存在着好几种千差万别的速度,即 1-10Hz 的总体机械响应速度、1-25 KHz 的内核控制器算法速度、10-50 MHz 的可编程逻辑运行速度,仿真运行时间从数分钟到数小时不等。我们可以借助一种对外设(PWM、电流感应和编码器处理)使用行为模型的控制环路模型解决这一问题,生成如图 3 所示的时间响应。

在使用控制环路模型微调控制器之后,下一步是使用包含外设的高保真度模型在仿真中证明控制器的合格性。方法是加入用于控制器的 C 和 HDL 组件的时序精度规格模型。这些规格模型拥有生成 C 和 HDL 代码所需的语义。通过仿真随后验证配备规格模型的系统能极为精确地追踪控制环路模型。

一旦性能使用高保真度模型验证完毕,接着在硬件中对控制器进行原型设计。根据图 1 所示的工作流程,首先从生成 IP 核入手。IP 核生成工作流程指导选择目标开发板,引导完成映射内核的输入和输出端口到目标接口的流程,包括 AXI4 接口和外部端口。

通过与 Vivado Design Suite 集成,该工作流程能完成比特流构建和 Zynq-7020 SoC 的架构编程。

现在 IP 核已经加载到目标器件上,下一步是从针对 ARM 内核的 Simulink 模型上生成嵌入式 C 语言代码。从生成 C 语言代码、编译 C 语言代码和用嵌入式 Linux 构建可执行文件整个过程完全自动化,然后原型即可投入运行。

为了运行原型硬件并验证其结果是否与仿真模型一致,我们构建了一个用作高级控制面板的修改版 Simulink 模型(图 4a)。在这个模型中删除了设备使用的仿真模型(即驱动电子电路、电机、负载和传感器部分),用连接到 ZedBoard 的 I/O 替代。

在 Simulink 会话中使用该模型可以启动电机,选择不同激励配置,监测相关信号,获取供在 MATLAB 中后续处理的数据,不过现在可以重复的是脉冲测试(图 3)。

图 4a 显示了硬件原型的轴转速和相流结果与仿真结果的对比情况。硬件原型的启动顺序与两个仿真模型的启动顺序有明显差别。不过这种情况的原因预计是硬件测试中电机的转子和定子的初始角与仿真中使用的初始角不同,导致电流控制算法在通过自己的编码器校准模式驱动电机时的响应不同。从施加脉冲第 2 秒开始,仿真和原型硬件的结果就基本完全吻合。

以这些结果为基础,可以继续进一步不同负载和运行条件下的测试,也可以开展进一步的 C 语言和 HDL 优化。

工程师正在转为使用基于模型的设计工作流程,在赛灵思 Zynq SoC 上实现算法的软硬件设计。Simulink 仿真能尽早评估算法,方便设计人员评估算法的有效性。无需实验室,在桌面上就能完成设计的权衡,显著提升生产力。业经验证的 C 语言和 HDL 代码生成技术,结合对赛灵思 All Programmable SoC 的硬件支持,为算法在真实硬件上运行提供快速且可重复的流程。仿真和硬件环境间的持续验证让设计人员能够在开发流程中尽早发现并解决问题。

MathWorks 为基于 Zynq 的开发板、软件定义无线电套件和电机控制套件提供工作流程支持。如需了解有关工作流程的更多信息,敬请访问:http://www.mathworks.com/zynq.

MATLAB 和 Simulink 均为The MathWorks公司的注册商标,详见: http://www.mathworks.com/trade- marks列出的其他商标。其他产品或品牌名称均为其各自所有者的商标或注册商标。